Протокол MSI - MSI protocol

В вычисление, то Протокол MSI - базовый протокол согласования кеш-памяти - работает в многопроцессорных системах. Как и в случае с другими протоколами когерентности кэша, буквы в имени протокола определяют возможные состояния, в которых может находиться строка кэша.

Обзор

В MSI каждый блок, содержащийся внутри кеша, может иметь одно из трех возможных состояний:

- Modified: Блок был изменен в тайник. В этом случае данные в кэше несовместимы с резервным хранилищем (например, объем памяти ). Кэш с блоком в состоянии «M» отвечает за запись блока в резервное хранилище, когда он вытесняется.

- Shared: этот блок не изменен и существует в состоянии только для чтения по крайней мере в одном кэше. Кэш может удалить данные, не записывая их в резервное хранилище.

- яnvalid: этот блок либо отсутствует в текущем кэше, либо был признан недействительным по запросу шины, и должен быть получен из памяти или другого тайник если блок должен храниться в этом кэше.[1]

Эти состояния согласованности поддерживаются посредством связи между кешами и резервным хранилищем. Кеши имеют разные обязанности, когда блоки читаются или записываются, или когда они узнают о других кэшах, выполняющих чтение или запись для блока.

Когда запрос чтения поступает в кэш для блока в состояниях «M» или «S», кэш предоставляет данные. Если блок не находится в кэше (в состоянии «I»), он должен проверить, что строка не находится в состоянии «M» в любом другом кэше. Различные архитектуры кэширования справляются с этим по-разному. Например, автобусные архитектуры часто работают шпионить, где запрос на чтение транслируется во все кеши. Другие архитектуры включают каталоги кеша у которых есть агенты (каталоги), которые знают, в каких кэшах последними были копии определенного блока кеша. Если другой кэш имеет блок в состоянии «M», он должен записать данные обратно в резервное хранилище и перейти в состояния «S» или «I». Как только любая строка «M» записана обратно, кэш получает блок либо из резервного хранилища, либо из другого кеша с данными в состоянии «S». Затем кеш может предоставить данные запрашивающей стороне. После подачи данных кэш-блок находится в состоянии «S».

Когда запрос на запись поступает в кэш для блока в состоянии «M», кэш изменяет данные локально. Если блок находится в состоянии «S», кэш должен уведомить любые другие кеши, которые могут содержать блок в состоянии «S», о том, что они должны удалить блок. Это уведомление может быть отправлено через отслеживание шины или через каталог, как описано выше. Затем данные могут быть изменены локально. Если блок находится в состоянии «I», кеш должен уведомить любые другие кеши, которые могут содержать блок в состояниях «S» или «M», что они должны удалить блок. Если блок находится в другом кэше в состоянии «M», этот кеш должен либо записать данные в резервное хранилище, либо передать их в запрашивающий кэш. Если в этот момент в кэше еще нет блока локально, блок считывается из резервного хранилища перед изменением в кеше. После изменения данных блок кэша находится в состоянии «M».

Для любой данной пары кешей допустимые состояния данной строки кэша следующие:

| M | S | я | |

|---|---|---|---|

| M | |||

| S | |||

| я |

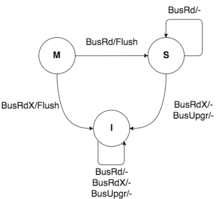

Государственный аппарат

Запросы процессора к кешу включают:

- PrRd: запрос процессора на чтение блока кэша.

- PrWr: запрос процессора на запись блока кэша.

Вдобавок есть запросы со стороны шины. Они включают:

- BusRd: когда в кеш-памяти процессора происходит промах при чтении, он отправляет запрос BusRd по шине и ожидает получить взамен блок кеша.

- BusRdX: когда в кэш процессора происходит промах при записи, он отправляет запрос BusRdX по шине, который возвращает блок кэша и делает недействительным блок в кешах других процессоров.

- BusUpgr: при попадании записи в кэш процессора он отправляет запрос BusUpgr на шину, чтобы сделать блок в кэше других процессоров недействительным.

- Flush: запрос, который указывает, что весь блок кеша записывается обратно в память.[2]

Переходы состояний:

- Недействительным:

- На PrRd выдается BusRd, и состояние изменяется на Общий.

- На PrWr выдается BusRdX и состояние изменяется на Изменено.

- На BusRd, BusRdX или BusUpgr остается недопустимый блок Недействительным.

- Общий:

- На PrRd блок остается в Общий штат.

- На PrWr выдается BusUpgr и состояние изменяется на Изменено.

- На BusRd блок остается в Общий штат.

- На BusRdX или BusUpgr блок переходит в Недействительным.

- Изменено:

- На PrRd или PrWr блок остается в Изменено штат.

- На BusRd блок кэша сбрасывается на шину, и состояние изменяется на Общий.

- На BusRdX блок кэша сбрасывается на шину, и состояние изменяется на Недействительным.[2]

- BusUpgr невозможен. Обратите внимание, что, находясь в Изменено состояние в одном конкретном процессоре, блок кеша должен находиться в Недействительным состояние во всех других процессорах, поскольку Изменено состояние допускается ни в одном процессоре или только в одном процессоре. Это эффективно исключает возможность наличия BusUpgr на шине, что потребует, чтобы этот блок находился в Общий состояние в одном из процессоров, который, как видно выше, выдает PrWr.

Применение

Этот протокол похож на тот, который используется в SGI 4D машина.[3]

Варианты

Современные системы используют варианты протокола MSI для уменьшения объема трафика в межсоединении когерентности. В Протокол MESI добавляет «эксклюзивное» состояние для уменьшения трафика, вызванного записью блоков, которые существуют только в одном кэше. В Протокол MOSI добавляет состояние «Принадлежит» для уменьшения трафика, вызванного обратной записью блоков, которые читаются другими кешами. В Протокол MOESI делает обе эти вещи.

Смотрите также

использованная литература

- ^ Фуксен, Р. (01.10.2010). «Как обратиться к сертификации для многоядерных платформ IMA: текущее состояние и потенциальные решения». Конференция по системам цифровой авионики (DASC), 29-е место, IEEE / AIAA, 2010 г.: 5.E.3–1-5.E.3-11. Дои:10.1109 / DASC.2010.5655461. ISBN 978-1-4244-6616-0.

- ^ а б Солихин, Ян (2016). Основы параллельной многоядерной архитектуры. Chapman & Hall / CRC Computational Science Series.

- ^ Су, Тэвён (декабрь 2006 г.). «ИНТЕГРАЦИЯ И ОЦЕНКА ПРОТОКОЛОВ КЕШЕВОЙ КОГЕРЕНТНОСТИ ДЛЯ МНОГОПРОЦЕССОРНЫХ SOCS» (PDF).