TurboSPARC - TurboSPARC

| |

| Общая информация | |

|---|---|

| Запущен | 1996 |

| Разработано | Fujitsu Microelectronics, Inc. |

| Спектакль | |

| Максимум. ЦПУ тактовая частота | От 160 МГц до 180 МГц |

| Архитектура и классификация | |

| Набор инструкций | SPARC V8 |

| Физические характеристики | |

| Ядра |

|

В TurboSPARC это микропроцессор который реализует SPARC V8 архитектура набора команд (ISA), разработанная Fujitsu Microelectronics, Inc. (FMI), американским филиалом японской многонациональной компании по производству оборудования и услуг в области информационных технологий. Fujitsu Limited находится в Сан-Хосе, Калифорния. Это был микропроцессор низкого уровня, изначально разработанный как модернизация для Sun Microsystems на базе microSPARC-II SPARCstation 5 рабочая станция. Он был представлен 30 сентября 1996 года с версией на 170 МГц по цене 499 долларов США в количестве 1000 штук.[1] TurboSPARC в основном преуспел на рынке SPARC начального уровня благодаря UltraSPARC IIi в конце 1997 г., но оставался доступным.

Пользователями TurboSPARC были Force Computers, Fujitsu, RDI Computer, Opus Systems, Tadpole Technologies, Tatung Science and Technology и Themis Computers. Fujitsu использовала версию 160 МГц в SPARCstation 5 комплект обновления, в то время как другие компании использовали версию 170 МГц в рабочих станциях, ноутбуках и встроенных компьютерах.

Производительность TurboSPARC 170 МГц была аналогична производительности 120 МГц. Intel Pentium, но по сравнению с microSPARC-II 110 МГц он имел в два раза большую производительность для целых чисел и в полтора раза производительность для операций с плавающей запятой.

Описание

TurboSPARC был простой скалярной структурой по порядку. На этапе выборки из 16-килобайтного кэша команд с прямым отображением были извлечены две инструкции. На этапе декодирования была декодирована одна инструкция, и ее операнды считывались из ее регистрового файла. Казнь началась на третьем этапе. TurboSPARC имел целочисленный блок и блок с плавающей запятой. Большинство целочисленных арифметических инструкций, за исключением умножения и деления, имеют задержку в один цикл. Умножение и деление выполнялось FPU. У Multiply была задержка в семь циклов, а у div - от 8 до 33 циклов. Большинство арифметических инструкций с плавающей запятой, за исключением операций деления и извлечения квадратного корня, имели задержку в четыре цикла.

Доступ к памяти происходит на четвертом этапе. TurboSPARC имеет кэш данных 16 КБ. Кэш имеет прямое отображение и использует политику обратной записи. При попадании в кэш данных данные возвращаются в том же цикле и проверяются на наличие ошибок на пятом этапе. Целочисленные результаты и нагрузки записываются в регистровый файл на шестом этапе. Команды с плавающей запятой, которые занимают больше циклов, завершаются на седьмом этапе и записываются в файл регистров с плавающей запятой на восьмом этапе.

TurboSPARC имеет встроенные контроллеры для кэш-памяти L2, памяти, интерфейса AFX и интерфейса SBus. Поддерживалась внешняя кэш-память L2 размером 256, 512 или 1 МБ. Кэш работал на половине или одной трети внутренней тактовой частоты: 85 или 56,67 МГц соответственно при 170 МГц. Он имел прямое отображение, имел размер строки 32 байта и использовал политику сквозной записи. Это было защищено паритетом. Кэш был построен из конвейерной пакетной статической оперативной памяти (PBSRAM) на 12 нс. Контроллер памяти поддерживает от 8 до 256 МБ режим быстрой страницы (FPM) DRAM в восьми банках. Доступ к кэш-памяти и памяти L2 осуществлялся с помощью системной шины, 72-битной шины, из которых 64 бита предназначались для данных.

Интерфейс AFX включил AFX видеокарты для прямого доступа к памяти. Он использует ту же шину данных, что и контроллеры кеша и памяти, но использует свои собственные линии управления. Контроллер SBus имел собственный буфер трансляции ввода / вывода на 16 записей. TurboSPARC поддерживается SBus частоты от 16,67 до 25 МГц. TurboSPARC не поддерживает работу с несколькими процессорами.

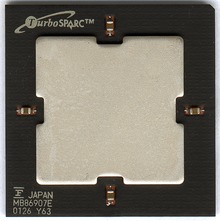

TurboSPARC содержал 3,0 миллиона транзисторов и имел размеры 11,5 на 11,5 мм при площади кристалла 132,25 мм.2.[2] Он был изготовлен Fujitsu в их процессе CS-60ALE, четырехуровневый металлический корпус толщиной 0,35 мкм. комплементарный металл – оксид – полупроводник (CMOS) процесс.[2] TurboSPARC был упакован в 416-шаровой пластиковая сетка для мячей (PBGA). Он использовал источник питания 3,3 В и имел максимальную рассеиваемую мощность 9 Вт.

Примечания

Рекомендации

- Fujitsu Microelectronics, Inc. (30 сентября 1996 г.). Новый процессор TurboSPARC Fujitsu Microelectronics устанавливает новый уровень производительности для рабочих станций низкого и среднего уровня. пресс-релиз.

- Гвеннап, Линли (18 ноября 1996 г.). «TurboSPARC предлагает модернизацию низкого уровня». Отчет микропроцессора С. 14–16.