Декодер адреса - Address decoder

В цифровая электроника, адресный декодер это двоичный декодер который имеет два или более входа для адрес биты и один или несколько выходов для сигналов выбора устройства.[1] Когда адрес для конкретного устройства появляется на адресных входах, декодер утверждает выход выбора для этого устройства. Выделенный декодер адреса с одним выходом может быть встроен в каждое устройство на шине адреса, или декодер с одним адресом может обслуживать несколько устройств.[2]

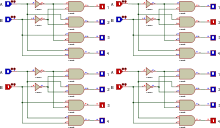

Один адресный декодер с n входными битами адреса может обслуживать до 2п устройств. Несколько членов 7400 серии из интегральные схемы могут использоваться как декодеры адресов. Например, при использовании в качестве декодера адреса 74154[3] обеспечивает четыре адресных входа и шестнадцать (т. е. 24) выходы селектора устройства. Декодер адреса - это частное использование двоичный декодер цепь, известная как "демультиплексор "или" демультиплексор "(74154 обычно называют" демультиплексором 4-в-16 "), который имеет много других применений помимо декодирования адреса.

Декодеры адресов являются фундаментальными строительными блоками для систем, использующих Автобусы. Они представлены во всех семействах и процессах интегральных схем и во всех стандартных FPGA и ASIC библиотеки. Они обсуждаются во вводных учебниках по цифровому логическому дизайну.[1]

использованная литература

- ^ а б Пол Горовиц и Winfield Hill (1989). Искусство электроники (2-е изд.). Издательство Кембриджского университета. п.685,766. ISBN 978-0-521-37095-0.

- ^ С. Дж. Кэхилл (1993). Цифровая и микропроцессорная техника (2-е изд.). Эллис Хорвуд. С. 489–494. ISBN 978-0-13-213398-2.

- ^ Лист данных 74HC154

внешние ссылки

| Эта компьютерное железо статья - это заглушка. Вы можете помочь Википедии расширяя это. |