Расширенный расширяемый интерфейс - Википедия - Advanced eXtensible Interface

В Расширенный расширяемый интерфейс (AXI), часть РУКА Расширенная архитектура шины микроконтроллера 3 (AXI3) и 4 (AXI4) спецификации,[1] это параллельно высокая производительность, синхронный, высокая частота, мульти-мастер, мульти-подчиненный коммуникация интерфейс, в основном предназначен для внутрикристальной коммуникации.

AXI был представлен в 2003 году со спецификацией AMBA3. В 2010 году новая версия AMBA, AMBA4, определила AXI4, AXI4-Lite и AXI4-Stream. протокол. AXI - это бесплатно и его спецификация находится в свободном доступе по адресу РУКА.

AXI предлагает широкий спектр функций, в том числе:

- отдельный адрес / этапы управления и данных

- поддержка невыровненного доступа к данным

- пакетные передачи, с однократной передачей стартового адрес

- отдельные и независимые каналы чтения и записи

- поддержка незавершенных транзакций

- поддержка завершения транзакций вне очереди для транзакций, имеющих разные идентификаторы потока на одном и том же главном порту. (Транзакции на одном и том же главном порту с одинаковым идентификатором потока должны выполняться по порядку. Кроме того, разные главные порты могут выполняться не по порядку относительно друг друга.)

- Поддержка для атомарные операции.

AMBA AXI определяет множество необязательных сигналы, которые могут быть опционально включены в зависимости от конкретных требований дизайна,[2] что делает AXI универсальной шиной для множества приложений.

Хотя общение через AXI автобус находится между одним ведущим и одним ведомым, спецификация включает подробное описание и сигналы для включения N: M межсоединений, способных расширить шину до топологий с большим количеством ведущих и ведомых устройств.[3]

AMBA AXI4, AXI4-Lite и AXI4-Stream были приняты Xilinx и многие из ее партнеров в качестве основных коммуникационных шин в своих продуктах.[4][5]

ID потоков

Идентификаторы потоков позволяют одному главному порту поддерживать несколько потоков, при этом каждый поток имеет упорядоченный доступ к адресному пространству AXI, однако каждый идентификатор потока, инициированный с одного главного порта, может завершаться не по порядку относительно друг друга. Например, в случае, когда один идентификатор потока заблокирован медленным периферийным устройством, другой идентификатор потока может продолжаться независимо от порядка идентификатора первого потока. Другой пример, одному потоку на процессоре может быть назначен идентификатор потока для доступа к памяти конкретного главного порта, такого как чтение addr1, запись addr1, чтение addr1, и эта последовательность будет завершена по порядку, потому что каждая транзакция имеет один и тот же идентификатор потока главного порта. Другой поток, работающий на процессоре, может иметь другой идентификатор потока главного порта, назначенный ему, и его доступ к памяти также будет в порядке, но может быть смешан с транзакциями с идентификаторами первого потока.

Идентификаторы потоков на главном порте не определены глобально, поэтому коммутатор AXI с несколькими главными портами будет внутренним префиксом индекса главного порта к идентификатору потока и предоставит этот объединенный идентификатор потока ведомому устройству, а затем при возврате транзакции на его мастер-порт происхождения, этот префикс идентификатора потока будет использоваться для определения местоположения главного порта, и префикс будет усечен. Вот почему идентификатор потока подчиненного порта в битах шире, чем идентификатор потока главного порта.

Шина Axi-lite - это шина AXI, которая поддерживает только один поток ID для каждого мастера. Эта шина обычно используется для конечной точки, которой необходимо одновременно обмениваться данными только с одним ведущим устройством, например, с простым периферийным устройством, таким как UART. Напротив, ЦП способен одновременно управлять несколькими периферийными устройствами и адресными пространствами и будет поддерживать более одного идентификатора потока на своих главных портах axi и подчиненных портах axi. Вот почему ЦП обычно поддерживает шину Axi с полной спецификацией. Типичный пример переключателя axi на передней панели может включать мастер-устройство axi с полной спецификацией, подключенное к мастеру процессора, и несколько подчиненных устройств axi-lite, подключенных к переключателю axi от различных периферийных устройств.

(Дополнительная шина axi-lite ограничена поддержкой длины транзакции только в 1 слово данных на транзакцию.)

Рукопожатие

AXI определяет базовый механизм рукопожатия, состоящий из сигналов xVALID и xREADY.[6] Сигнал xVALID управляется источником, чтобы сообщить объекту назначения, что полезная нагрузка на канале действительна и может быть прочитана из этого такт вперед. Точно так же сигнал xREADY запускается принимающим объектом, чтобы уведомить, что он готов к приему данных.

Когда оба сигнала xVALID и xREADY имеют высокий уровень такт, полезная нагрузка данных считается "переданной", и источник может либо предоставить новую полезную нагрузку, поддерживая высокий xVALID, либо прекратить передачу, отменив xVALID. Индивидуальная передача данных, поэтому тактовый цикл, когда и xVALID, и xREADY имеют высокий уровень, называется "биением".

Для управления этими сигналами определены два основных правила:

- Источник не должен ждать высокого уровня xREADY для подтверждения xVALID.

- После утверждения источник должен поддерживать высокий xVALID до тех пор, пока не произойдет рукопожатие.

Благодаря этому рукопожатие Механизм, как источник, так и место назначения могут контролировать поток данных, при необходимости регулируя скорость.

каналы

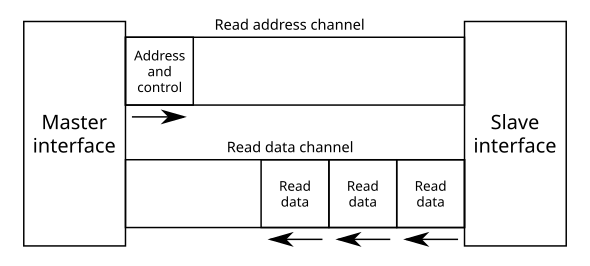

В спецификации AXI пять каналы описаны:[7]

- Чтение адресного канала (AR)

- Чтение канала данных (R)

- Канал записи адреса (AW)

- Канал записи данных (Вт)

- Канал ответа на запись (B)

Помимо некоторых основных правил заказа,[8] каждый канал независимы друг от друга и имеют свою пару xVALID / xREADY рукопожатие сигналы.[9]

AXI

Сигналы

| Описание сигнала | Написать адресный канал | Читать адресный канал |

|---|---|---|

| Идентификатор адреса для идентификации нескольких потоки за один канал | AWID | ARID |

| Адрес первой доли очереди | AWADDR | ARADDR |

| Количество ударов внутри пакета | AWLEN[nb 1] | АРЛЕН[nb 1] |

| Размер каждой доли | AWSIZE | ARSIZE |

| Тип взрыва | AWBURST | АРБЕРСТ |

| Тип замка, чтобы обеспечить атомарные операции | AWLOCK[nb 1] | АРЛОК[nb 1] |

| Тип памяти, как транзакция должна проходить через систему | AWCACHE | ARCACHE |

| Тип защиты: привилегия, уровень безопасности и доступ к данным / инструкциям | АВПРОТ | ARPROT |

| Качество обслуживания сделки | AWQOS[nb 2] | ARQOS[nb 2] |

| Идентификатор региона для доступа к нескольким логическим интерфейсам с одного физического | AWREGION[nb 2] | ОБЛАСТЬ[nb 2] |

| Пользовательские данные | AWUSER[nb 2] | ARUSER[nb 2] |

| xVALID рукопожатие сигнал | НЕДЕЙСТВИТЕЛЬНО | АРВАЛИД |

| xREADY рукопожатие сигнал | УДИВИТЕЛЬНО | ЗАВЕРШАЕТСЯ |

| Описание сигнала | Запись канала данных | Чтение канала данных |

|---|---|---|

| Идентификатор данных, чтобы идентифицировать несколько потоки за один канал | WID[№ 3] | ИЗБАВЛЯТЬ |

| Чтение / запись данных | WDATA | RDATA |

| Прочитать ответ, чтобы указать статус текущего сигнала RDATA | RRESP | |

| Байт строб, чтобы указать, какие байты сигнала WDATA действительны | WSTRB | |

| Идентификатор последней доли | WLAST | RLAST |

| Пользовательские данные | WUSER[nb 2] | РУСЕР[nb 2] |

| xVALID рукопожатие сигнал | WVALID | RVALID |

| xREADY рукопожатие сигнал | ПОДГОТОВКА | НАСТОЯЩИЙ |

| Описание сигнала | Написать канал ответа |

|---|---|

| Запишите идентификатор ответа, чтобы идентифицировать несколько потоки за один канал | ДЕЛАТЬ СТАВКУ |

| Напишите ответ, чтобы указать статус пакета | БРЕСП |

| Пользовательские данные | БУСЕР[nb 2] |

| xVALID рукопожатие сигнал | BVALID |

| xREADY рукопожатие сигнал | ХЛЕБ |

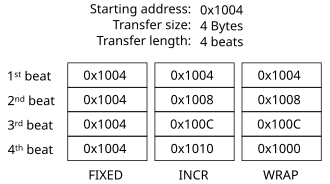

Всплески

AXI - это пакетный протокол,[11] Это означает, что для одного запроса может быть несколько передач данных (или битов). Это делает его полезным в случаях, когда необходимо передать большой объем данных от или к определенному шаблону адресов. В AXI пакеты могут быть трех типов, выбранных сигналами ARBURST (для чтения) или AWBURST (для записи ):[12]

- ФИКСИРОВАННЫЙ

- INCR

- СВОРАЧИВАТЬ

В ФИКСИРОВАННЫХ пакетах каждый такт в передаче имеет один и тот же адрес. Это полезно для повторного доступа к одной и той же ячейке памяти, например, при чтении или записи ФИФО.

С другой стороны, в пакетах INCR каждый бит имеет адрес, равный предыдущему, плюс размер передачи. Этот тип пакета обычно используется для чтения или записи последовательных областей памяти.

Пакеты WRAP аналогичны пакетам INCR, поскольку каждая передача имеет адрес, равный предыдущему, плюс размер передачи. Однако с пакетами WRAP, если адрес текущего удара достигает «границы верхнего адреса», он сбрасывается до «границы переноса»:

с

Сделки

Читает

Чтобы начать транзакцию чтения, мастер должен предоставить в канале адреса чтения:

- начальный адрес на ARADDR

- тип пакета, FIXED, INCR или WRAP, на ARBURST (если есть)

- длина пакета на ARLEN (если есть).

Кроме того, другие вспомогательные сигналы, если они есть, используются для определения более конкретных передач.

После обычного рукопожатия ARVALID / ARREADY ведомое устройство должно предоставить на канале чтения данных:

- данные, соответствующие указанному адресу (ам) на RDATA

- статус каждой доли на RRESP

плюс любые другие дополнительные сигналы. Каждый такт ответа ведомого выполняется с помощью рукопожатия RVALID / RREADY, и при последней передаче ведомое устройство должно подтвердить RLAST, чтобы сообщить, что больше тактов не последует без нового запроса на чтение.

Пишет

Чтобы начать операцию записи, мастер должен предоставить как адресную информацию, так и данные.

Информация об адресе предоставляется по каналу адреса записи аналогично операции чтения:

- начальный адрес должен быть указан на AWADDR

- тип пакета, FIXED, INCR или WRAP, на AWBURST (если присутствует)

- длина пакета на AWLEN (если есть)

и, если есть, все дополнительные сигналы.

Мастер также должен предоставить данные, относящиеся к указанному адресу (адресам) в канале данных записи:

- данные по WDATA

- биты «строба» в WSTRB (если они есть), которые условно помечают отдельные байты WDATA как «действительные» или «недействительные»

Как и в пути чтения, в последнем слове данных мастер должен подтвердить WLAST.

После завершения обеих транзакций ведомое устройство должно отправить обратно ведущему устройству состояние записи по каналу ответа записи, возвращая результат по сигналу BRESP.

AXI4-Lite

AXI4-Lite - это подмножество протокола AXI4, обеспечивая регистрационный структура с уменьшенными функциями и сложностью.[14] Заметные отличия:

- все пакеты состоят только из 1 доли

- все обращения к данным используют полную ширину шины данных, которая может быть 32 или 64 бит

AXI4-Lite удаляет часть сигналов AXI4, но следует спецификации AXI4 для остальных. Быть подмножество транзакций AXI4, AXI4-Lite полностью совместимы с устройствами AXI4, что позволяет совместимость между ведущими устройствами AXI4-Lite и ведомыми устройствами AXI4 без дополнительной логики преобразования.[15]

Сигналы

| Написать адресный канал | Запись канала данных | Написать канал ответа | Читать адресный канал | Чтение канала данных |

|---|---|---|---|---|

| НЕДЕЙСТВИТЕЛЬНО | WVALID | BVALID | АРВАЛИД | RVALID |

| УДИВИТЕЛЬНО | ПОДГОТОВКА | ХЛЕБ | ЗАВЕРШАЕТСЯ | НАСТОЯЩИЙ |

| AWADDR | WDATA | БРЕСП | ARADDR | RDATA |

| АВПРОТ | WSTRB | ARPROT | RRESP |

Смотрите также

- Расширенная архитектура шины микроконтроллера

- Wishbone (компьютерный автобус)

- Мастер / подчиненный (технология)

Рекомендации

- ^ «AMBA | Документация». Arm Holdings.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 109–118. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 23–24. Получено 5 июля 2019.

- ^ «Протокол интерфейса AMBA AXI4». www.xilinx.com. Xilinx Inc.

- ^ «AXI4 IP». www.xilinx.com. Xilinx Inc.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 37–38. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 22–23. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. п. 40. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. п. 38. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 28–34. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. п. 22. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 45–47. Получено 5 июля 2019.

- ^ а б Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. п. 44. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. стр. 121–128. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. п. 124. Получено 5 июля 2019.

- ^ Arm Holdings. «Спецификация протокола AMBA AXI и ACE» (PDF). developer.arm.com. п. 122. Получено 5 июля 2019.