Интегрирующий АЦП - Integrating ADC

An интегрирующий АЦП это тип аналого-цифровой преобразователь который преобразует неизвестное входное напряжение в цифровое представление с помощью интегратор. В его базовой реализации, преобразователе с двойным наклоном, неизвестное входное напряжение подается на вход интегратора и может возрастать в течение фиксированного периода времени (период разгона). Тогда известное опорное напряжение противоположной полярности подается на интегратор и ей дает сползать до выходных возвращаются интегратора к нулю (выбег периода). Входное напряжение вычисляются как функция опорного напряжения, постоянного разбегом период времени, и измеренный захудалого период времени. Измерение времени выбега обычно производится в тактовых единицах преобразователя, поэтому более длительное время интегрирования обеспечивает более высокое разрешение. Точно так же скорость преобразователя может быть улучшена за счет уменьшения разрешения.

Преобразователи этого типа могут достигать высокого разрешения, но часто это достигается за счет скорости. По этой причине эти преобразователи не используются в приложениях для обработки звука или сигналов. Их использование обычно ограничивается цифровыми вольтметрами и другими приборами, требующими высокоточных измерений.

Основной дизайн

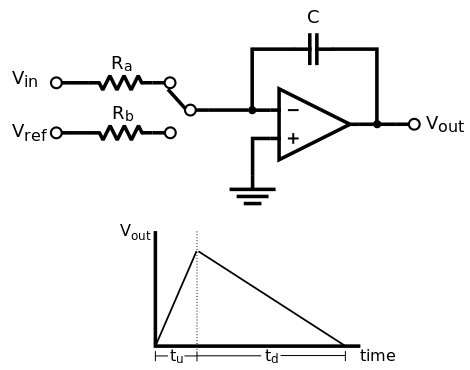

Основная интегрируя схема АЦП состоит из интегратора, переключатель для выбора между напряжением измеряемого и опорного напряжения, таймер, который определяет, как долго интегрировать неизвестные и меры, как долго ссылка интеграции принял, компаратор для обнаружения пересечения нуля , и контроллер. В зависимости от реализации, переключатель может также присутствовать параллельно с конденсатором интегратора, чтобы обеспечить возможность сброса интегратора. Входы в контроллер включают часы (используемые для измерения времени) и выход компаратора, используемый для определения, когда выход интегратора достигает нуля.

Превращение происходит в два этапа: этап разбег, где вход интегратора напряжения, подлежащего измерению, и выбега фазы, в котором вход интегратора является известным опорным напряжением. Во время фазы разгона переключатель выбирает измеренное напряжение в качестве входа для интегратора. Интегратору дают возможность нарастать в течение фиксированного периода времени, чтобы позволить заряду на конденсаторе интегратора. Во время фазы запуска вниз, то переключатель выбирает опорное напряжение в качестве входного сигнала интегратора. На этом этапе измеряется время, необходимое для возврата выходного сигнала интегратора к нулю.

Для того, чтобы опорное напряжение для постепенного изменения вниз интегратора напряжения, потребности опорного напряжения, чтобы иметь полярность, противоположную полярности входного напряжения. В большинстве случаев для положительных входных напряжений, это означает, что опорное напряжение будет отрицательным. Для того, чтобы обрабатывать как положительные, так и отрицательные входные напряжения, требуется положительное и отрицательное опорное напряжение. Выбор эталона для использования во время фазы разгона будет основан на полярности выхода интегратора в конце фазы разгона.

Основное уравнение для выхода интегратора (при условии постоянного входа):

Предполагая, что начальное напряжение интегратора в начале каждого преобразования равно нулю и что напряжение интегратора в конце периода выбега будет равно нулю, мы имеем следующие два уравнения, которые покрывают выход интегратора во время двух фаз преобразования:

Два уравнения можно объединить и решить для , неизвестное входное напряжение:

Из уравнения становится очевидным одно из преимуществ интегрирующего АЦП с двойным наклоном: измерение не зависит от значений элементов схемы (R и C). Однако это не означает, что значения R и C не важны при разработке интегрирующего АЦП с двойным наклоном (как будет объяснено ниже).

Обратите внимание, что на графике справа напряжение показано как повышающееся во время фазы разгона и снижающееся во время фазы выбега. В действительности, поскольку интегратор использует операционный усилитель в конфигурации с отрицательной обратной связью, применяя положительный заставит выход интегратора пойти вниз. В вверх и вниз более точно относится к процессу добавления заряда к конденсатору интегратора во время фазы разгона и удаления заряда во время фазы выбега.

Разрешающая способность интегрирующего АЦП с двойным наклоном определяется в первую очередь длительностью периода выбега и разрешением измерения времени (т. Е. Частотой тактовых импульсов контроллера). Требуемое разрешение (в количестве бит) определяет минимальную длину периода выбега для полномасштабного входа ():

Во время измерения входного сигнала полной шкалы наклон выходного сигнала интегратора будет одинаковым во время фаз разгона и выбега. Это также означает, что время периода разгона и периода выбега будет равным () и что общее время измерения будет . Следовательно, общее время измерения для полномасштабного входа будет основано на желаемом разрешении и частоте тактовых импульсов контроллера:

Если требуется разрешение в 16 бит при тактовой частоте контроллера 10 МГц, время измерения будет 13,1 миллисекунды (или частота дискретизации всего 76 выборок в секунду). Однако время выборки можно уменьшить, жертвуя разрешением. Если требование к разрешающей способности уменьшается до 10 бит, время измерения также сокращается до 0,2 миллисекунды (почти 4900 выборок в секунду).

Ограничения

Существуют ограничения на максимальное разрешение интегрирующего АЦП с двойным наклоном. Невозможно увеличить разрешение базового двухканального АЦП до произвольно высоких значений за счет увеличения времени измерения или более быстрой тактовой частоты. Разрешение ограничено:

- Диапазон интегрирующего усилителя. Рейки напряжения на операционном усилителе ограничивают выходное напряжение интегратора. Вход, оставленный подключенным к интегратору слишком долго, в конечном итоге приведет к тому, что операционный усилитель ограничит свой выход некоторым максимальным значением, что сделает любые вычисления на основе времени выбега бессмысленными. резистор интегратора и конденсатор, таким образом, выбраны тщательно основаны на рельсах напряжения операционного усилителя, опорного напряжения и ожидаемого ввода полной шкалы, и долгое время разгона, необходимого для достижения нужного разрешения.

- Точность компаратора, используемого в качестве детектора нуля. Широкополосный шум схемы ограничивает способность компаратора точно определять, когда выходной сигнал интегратора достигает нуля. Гёке предлагает типичным пределом разрешающей способности компаратора 1 милливольт.[1]

- Качество конденсатора интегратора. Хотя интегрирующий конденсатор не обязательно должен быть идеально линейным, он должен быть неизменным во времени. Диэлектрическое поглощение вызывает ошибки линейности.[2]

Улучшения

Базовая конструкция интегрирующего АЦП с двумя характеристиками имеет ограничения по линейности, скорости преобразования и разрешающей способности. В базовую конструкцию был внесен ряд модификаций, чтобы до некоторой степени их преодолеть.

Предварительные улучшения

Улучшенный двойной наклон

Фаза разгона базовой конструкции с двойным наклоном интегрирует входное напряжение в течение фиксированного периода времени. То есть это позволяет неизвестному количеству заряда накапливаться на конденсаторе интегратора. Затем фаза выбега используется для измерения этого неизвестного заряда для определения неизвестного напряжения. Для ввода полной шкалы равного опорного напряжения, половина времени измерения проводится в фазе разгона. Сокращение времени, затрачиваемого на фазу запуска, может уменьшить общее время измерения. Общая реализация использует входной диапазон вдвое больше, чем опорное напряжение.

Простой способ сократить время разгона - увеличить скорость накопления заряда на конденсаторе интегратора за счет уменьшения размера резистора, используемого на входе. Это по-прежнему позволяет накапливать тот же общий объем заряда, но за меньший период времени. Использование того же алгоритма для фазы выбега приводит к следующему уравнению для расчета неизвестного входного напряжения ():

Обратите внимание, что это уравнение, в отличие от уравнения для базового преобразователя с двойным наклоном, имеет зависимость от номиналов резисторов интегратора. Или, что еще более важно, он зависит от соотношение двух значений сопротивления. Эта модификация ничего не делает для улучшения разрешения преобразователя (поскольку не устраняет ни одно из ограничений разрешения, указанных выше).

Многоклонный разбег

Один из способов улучшить разрешающую способность преобразователя - искусственно увеличить диапазон интегрирующего усилителя во время фазы разгона. Как упоминалось выше, цель фазы разгона состоит в том, чтобы добавить неизвестное количество заряда интегратору, которое впоследствии будет измерено во время фазы выбега. Возможность добавления большего количества заряда позволяет проводить измерения с более высоким разрешением. Например, предположим, что мы можем измерить заряд интегратора во время фазы выбега с точностью до 1 кулон. Если наш усилитель интегратора ограничивает нас возможностью добавить к интегратору только до 16 кулонов заряда во время фазы разгона, наше общее измерение будет ограничено 4 битами (16 возможных значений). Если мы сможем увеличить диапазон интегратора, чтобы мы могли добавить до 32 кулонов, разрешение нашего измерения увеличится до 5 бит.

Один из методов увеличения емкости интегратора - это периодическое добавление или вычитание известных величин заряда во время фазы разгона, чтобы поддерживать выходной сигнал интегратора в пределах диапазона усилителя интегратора. Тогда общая сумма искусственно накопленного заряда - это заряд, внесенный неизвестным входным напряжением, плюс сумма известных зарядов, которые были добавлены или вычтены.

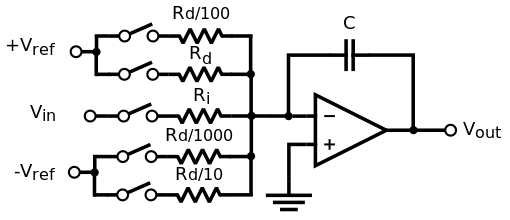

Принципиальная схема, показанная справа, является примером того, как можно реализовать многоканальный разбег. Идея состоит в том, что неизвестное входное напряжение, , всегда применяется к интегратору. Положительные и отрицательные опорные напряжения, контролируемые двумя независимыми переключателями, добавляют и вычитают заряд по мере необходимости, чтобы поддерживать выходной сигнал интегратора в его пределах. Эталонные резисторы, и обязательно меньше, чем чтобы ссылки могли преодолеть заряд, вносимый вводом. А компаратор подключен к выходу для сравнения напряжения интегратора с пороговым напряжением. Выход компаратора используется контроллером преобразователя, чтобы решить, какой источник опорного напряжения должен быть применен. Это может быть относительно простой алгоритм: если выход интегратора выше порога, разрешите положительное задание (чтобы снизить выход); если выход интегратора ниже порога, включите отрицательное задание (чтобы увеличить выход). Контроллер отслеживает, как часто включается каждый переключатель, чтобы оценить, сколько дополнительного заряда было помещено на (или снято с него) конденсатор интегратора в результате опорных напряжений.

Справа приведен график выборки выходного сигнала интегратора во время многократного разгона. Каждая пунктирная вертикальная линия представляет собой точку принятия решения контроллера, где он образцы полярности выходного сигнала и выбирает для применения либо положительной или отрицательного опорного напряжения на вход. В идеале выходное напряжение интегратора в конце периода разгона можно представить следующим уравнением:

куда период выборки, - количество периодов, в течение которых включается положительное задание, - количество периодов, в течение которых включается отрицательное задание, и - общее количество периодов в фазе разгона.

Разрешение, полученное во время периода разгона, можно определить, сделав предположение, что выходной сигнал интегратора в конце фазы разгона равен нулю. Это позволяет нам связать неизвестный вход, , только ссылки и значения:

Разрешающую способность можно выразить через разницу между отдельными шагами на выходе преобразователя. В этом случае, если мы решим указанное выше уравнение для с помощью и (сумма и всегда должен равняться ), разница будет равна наименьшей разрешаемой величине. Это приводит к уравнению для разрешения многосклонной фазы разгона (в битах):

Использование типовых значений эталонных резисторов и 10 кОм и входной резистор 50 кОм, мы можем достичь 16-битного разрешения во время фазы разгона с 655360 периодами (65,5 миллисекунд при тактовой частоте 10 МГц).

Несмотря на то, что можно продолжать многократный разбег неограниченно долго, невозможно повысить разрешающую способность преобразователя до произвольно высоких уровней, просто используя более длительное время разгона. Ошибка вносится в разгон по нескольким параметрам из-за действия переключателей, управляющих эталонами, перекрестной связи между переключателями, непреднамеренной инжекции заряда переключателя, несоответствий в эталонах и ошибок синхронизации.[3]

Отчасти эту ошибку можно уменьшить осторожным обращением с переключателями.[4][5] В частности, во время периода разгона каждый переключатель должен срабатывать постоянное количество раз. Алгоритм, описанный выше, этого не делает, а просто переключает переключатели по мере необходимости, чтобы поддерживать выход интегратора в установленных пределах. При активировании каждого переключателя постоянное количество раз ошибка, связанная с переключением, становится примерно постоянной. Любое выходное смещение, являющееся результатом ошибки переключения, можно измерить и затем вычесть из результата.

Эксплуатационные улучшения

Многосклонный спуск

Простой односторонний спуск проходит медленно. Обычно время останова измеряется в тактах часов, поэтому для получения четырехзначного разрешения время останова может занять до 10 000 тактов. Многогранный спуск может ускорить измерение без ущерба для точности. Используя 4 скорости нарастания, каждая из которых в десять раз более постепенна, чем предыдущая, четырехзначное разрешение может быть достигнуто примерно за 40 или меньше тактов часов - огромное улучшение скорости.[6]

Схема, показанная справа, является примером многоскатной схемы спуска с четырьмя спусками, каждый из которых в десять раз более плавный, чем предыдущий. Переключатели определяют, какой наклон выбран. Переключатель, содержащий выбирает самый крутой наклон (то есть заставляет выход интегратора двигаться к нулю быстрее всего). В начале интервала выбега неизвестный вход удаляется из схемы путем размыкания переключателя, подключенного к и закрытие выключатель. Как только выход интегратора достигает нуля (и измеряется время выбега), переключатель открывается, и следующий наклон выбирается путем закрытия выключатель. Это повторяется до финального наклона достиг нуля. Комбинация времени выбега для каждого из наклонов определяет значение неизвестного входа. По сути, каждый наклон добавляет к результату одну цифру разрешения.

В примере схемы резисторы наклона различаются в 10 раз. Это значение, известное как основание (), может иметь любое значение. Как поясняется ниже, выбор базы влияет на скорость преобразователя и определяет количество наклонов, необходимых для достижения желаемого разрешения.

В основе этой схемы лежит допущение, что при попытке найти переход через нуль в конце интервала выбега всегда будет иметь место выброс. Это обязательно будет верно, учитывая любой гистерезис на выходе компаратора, измеряющего переход через нуль, и из-за периодической выборки компаратора на основе часов преобразователя. Если мы предположим, что преобразователь переключается с одного наклона на другой за один тактовый цикл (что может быть, а может и не быть возможным), максимальная величина выброса для данного наклона будет самым большим изменением выходного сигнала интегратора за один тактовый период:

Чтобы преодолеть это перерегулирование, следующий наклон потребует не более тактовые циклы, что помогает установить ограничение на общее время выбега. Время для первого выбега (с использованием самого крутого спада) зависит от неизвестного входа (т. Е. Количества заряда, помещенного на конденсатор интегратора во время фазы разгона). В лучшем случае это будет:

куда - максимальное количество тактовых периодов для первого наклона, - максимальное напряжение интегратора в начале фазы выбега, а резистор, используемый для первого наклона.

Остальные наклоны имеют ограниченную продолжительность в зависимости от выбранной базы, поэтому оставшееся время преобразования (в тактовых периодах преобразователя) составляет:

куда количество наклонов.

Преобразование измеренных временных интервалов во время многоскатного разгона в измеренное напряжение аналогично методу балансировки заряда, используемому в улучшении многоскатного разгона. Каждый наклон добавляет или вычитает известное количество заряда конденсатора интегратора. В результате разгона интегратору будет добавлена неизвестная сумма заряда. Затем во время выбега первый наклон вычитает большое количество заряда, второй наклон добавляет меньшее количество заряда и т. Д., Причем каждый последующий наклон перемещается на меньшую величину в направлении, противоположном предыдущему наклону с целью все ближе и ближе к нулю. Каждый наклон добавляет или вычитает количество заряда, пропорциональное сопротивлению наклона и продолжительности наклона:

обязательно является целым числом и будет меньше или равно для второго и последующих спусков. Используя приведенную выше схему в качестве примера, второй наклон, , может внести следующую плату, , интегратору:

- в шагах от

То есть, возможные значения, при этом наибольшее значение равно наименьшему шагу первого наклона или одна цифра (основание 10) разрешения на наклон. Обобщая это, мы можем представить количество наклонов, , с точки зрения базы и требуемого разрешения, :

Подставляя это обратно в уравнение, представляющее время выбега, необходимое для второго и последующих уклонов, мы получаем следующее:

Что, при оценке, показывает, что минимальное время выбега может быть достигнуто с использованием базы е. Эту базу может быть сложно использовать как с точки зрения сложности расчета результата, так и с точки зрения поиска подходящей цепи резисторов, поэтому база из 2 или 4 будет более распространенной.

Остаточный ADC

При использовании усовершенствований разгона, таких как разгон с несколькими накатами, когда часть разрешения преобразователя решается во время фазы разгона, можно полностью исключить фазу выбега, используя второй тип аналогового в цифровой преобразователь.[7] В конце фазы разгона многоскоростного преобразования на конденсаторе интегратора все еще будет оставаться неизвестное количество заряда. Вместо использования традиционной фазы разгона для определения этого неизвестного заряда неизвестное напряжение может быть преобразовано непосредственно вторым преобразователем и объединено с результатом фазы разгона для определения неизвестного входного напряжения.

Предполагая, что используется многократный разбег, как описано выше, неизвестное входное напряжение может быть связано со счетчиками многоскатного разгона, и , и измеренное выходное напряжение интегратора, используя следующее уравнение (полученное из выходного уравнения многосклонного разгона):

Это уравнение представляет собой теоретический расчет входного напряжения с учетом идеальных компонентов. Поскольку уравнение зависит почти от всех параметров схемы, любые отклонения опорных токов, конденсатора интегратора или других значений приведут к ошибкам в результате. Коэффициент калибровки обычно включается в термин для учета измеренных ошибок (или, как описано в указанном патенте, для преобразования выходного сигнала АЦП остатка в единицы счетчиков разгона).

Вместо того, чтобы полностью исключить фазу выбега, ADC остатка также можно использовать для повышения точности фазы спада, чем это было бы возможно в противном случае.[8] При традиционной фазе выбега период измерения времени выбега заканчивается, когда выход интегратора пересекает нулевое напряжение. При обнаружении перехода через нуль с помощью компаратора возникает определенная погрешность (один из недостатков базовой конструкции с двойным наклоном, как описано выше). Используя остаточный АЦП для быстрой выборки выходного сигнала интегратора (например, синхронизированного с часами контроллера преобразователя), показание напряжения может быть снято как непосредственно до, так и сразу после перехода через нуль (при измерении с помощью компаратора).Поскольку наклон напряжения интегратора постоянен во время фазы выбега, два измерения напряжения могут использоваться в качестве входных данных для функции интерполяции, которая более точно определяет время перехода через нуль (т. Е. С гораздо более высоким разрешением, чем одни только часы контроллера позволят).

Прочие улучшения

Конвертер с непрерывной интеграцией

Комбинируя некоторые из этих усовершенствований базовой конструкции с двойным наклоном (а именно, многосклонный разбег и остаточный АЦП), можно построить интегрирующий аналого-цифровой преобразователь, способный работать непрерывно без необходимости интервал выбега.[9] Концептуально алгоритм разгона с несколькими уклонами может работать непрерывно. Чтобы начать преобразование, одновременно происходят две вещи: остаточный АЦП используется для измерения приблизительного заряда в настоящее время на конденсаторе интегратора, и счетчики, отслеживающие многоскадный скачок, сбрасываются. В конце периода преобразования снимается еще одно остаточное показание АЦП и записываются значения многоскоростных счетчиков разгона.

Неизвестный вход рассчитывается с использованием аналогичного уравнения, которое используется для остаточного АЦП, за исключением того, что учитываются два выходных напряжения ( представляющее измеренное напряжение интегратора в начале преобразования, и представляющее измеренное напряжение интегратора в конце преобразования.

Такой непрерывно интегрирующий преобразователь очень похож на дельта-сигма аналого-цифровой преобразователь.

Калибровка

В большинстве вариантов интегрирующего преобразователя с двойным наклоном характеристики преобразователя зависят от одного или нескольких параметров схемы. В случае основной конструкции, выход преобразователя в терминах опорного напряжения. В более продвинутых конструкциях также есть зависимости от одного или нескольких резисторов, используемых в схеме, или от используемого конденсатора интегратора. Во всех случаях, даже при использовании дорогостоящих прецизионных компонентов, могут быть другие эффекты, которые не учитываются в общих уравнениях двойного наклона (диэлектрический эффект на конденсаторе или частотные или температурные зависимости любого из компонентов). Любая из этих вариаций приводит к ошибке на выходе преобразователя. В лучшем случае это просто ошибка усиления и / или смещения. В худшем случае это может привести к нелинейности или немонотонности.

Некоторая калибровка может выполняться внутри преобразователя (т. Е. Не требуя какого-либо специального внешнего входа). Этот тип калибровки будет выполняться каждый раз при включении преобразователя, периодически во время работы преобразователя или только при входе в специальный режим калибровки. Другой тип калибровки требует внешних вводов известных величин (например, стандарты напряжения или прецизионные эталоны сопротивления) и обычно выполняются нечасто (каждый год для оборудования, используемого в нормальных условиях, чаще при использовании в метрология Приложения).

Из этих типов ошибок проще всего исправить ошибку смещения (при условии, что смещение постоянное во всем диапазоне преобразователя). Часто это делается внутри самого преобразователя путем периодического измерения потенциала земли. В идеале измерение земли всегда должно давать нулевой выходной сигнал. Любой ненулевой выходной сигнал указывает на ошибку смещения в преобразователе. То есть, если измерение заземления дало выходное напряжение 0,001 вольт, можно предположить, что все измерения будут смещены на одинаковую величину, и можно вычесть 0,001 из всех последующих результатов.

Погрешность усиления аналогичным образом может быть измерена и скорректирована изнутри (опять же при условии, что существует постоянная ошибка усиления во всем диапазоне выходных сигналов). Опорное напряжение (или некоторое напряжение, получаемое непосредственно из ссылки), может быть использовано в качестве входных данных для преобразователя. Если предполагается, что эталонное напряжение является точным (в пределах допусков преобразователя) или что эталонное напряжение было откалибровано извне по эталону напряжения, любая ошибка в измерении будет ошибкой усиления в преобразователе. Если, например, измерение 5 вольтой ссылки преобразовательной привело в выходе 5,3 вольт (после учета каких-либо ошибок смещения), коэффициент усилените умножитель 0,94 (5 / 5,3) может быть применены к любым последующим результатам измерений.

Смотрите также

Сноски

- ^ Гёке 1989, п. 9

- ^ Каталог Hewlett-Packard, 1981, стр. 49, где говорится: «Для небольших входов шум становится проблемой, а для больших входов диэлектрическое поглощение конденсатора становится проблемой».

- ^ Энг и Матсон 1994

- ^ Энг и Матсон 1994

- ^ Гёке 1989

- ^ Гёке 1989, п. 9, в котором говорится: «Многократное повторение сокращает время выполнения цикла».

- ^ Ридель 1992

- ^ Regier 2001

- ^ Гёке 1992

Рекомендации

- США 5321403, Eng, Benjamin, Jr. & Don Matson, "Аналого-цифровой преобразователь с множественным наклоном", опубликованный 14 июня 1994 г.

- Гёке, Уэйн (апрель 1989 г.), «8,5-разрядный интегрирующий аналого-цифровой преобразователь с 16-разрядной производительностью 100 000 выборок в секунду» (PDF), Журнал HP, 40 (2): 8–15

- США 5117227, Goeke, Wayne, "Постоянно интегрируемый аналого-цифровой преобразователь высокого разрешения", выпущенный 26 мая 1992 г.

- Кестер, Уолт, Справочник по преобразованию данных, ISBN 0-7506-7841-0

- США 6243034, Регье, Кристофер, «Интеграция аналого-цифрового преобразователя с улучшенным разрешением», выпущенный 5 июня 2001 г.

- США 5101206, Ридель, Рональд, "Интеграция аналого-цифрового преобразователя", выпущенный 31 марта 1992 г.