Задержка распространения - Propagation delay

Задержка распространения - время, необходимое сигналу для достижения пункта назначения. Это может относиться к сеть, электроника или физика. Время удержания - это минимальный интервал, необходимый для того, чтобы логический уровень оставался на входе после запуска фронта тактового импульса.

Сети

В компьютерная сеть, задержка распространения - это время, необходимое для прохождения заголовка сигнала от отправителя к получателю. Его можно вычислить как отношение между длиной линии и скоростью распространения в конкретной среде.

Задержка распространения равна д / с где d это расстояние и s это скорость распространения волны. В беспроводной связи s=c, т.е. скорость света. В медная проволока, скорость s обычно колеблется от 0,59С до 0,77С.[1][2] Эта задержка является основным препятствием в разработке высокоскоростных компьютеров и называется узкое место в межсоединении в системах IC.

Электроника

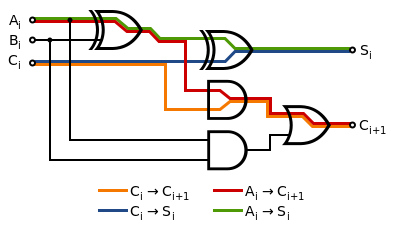

В электроника, цифровые схемы и цифровая электроника, задержка распространения, или задержка ворот, - это промежуток времени, который начинается, когда вход в логический вентиль становится стабильным и допустимым для изменения до того момента, когда выход этого логического элемента станет стабильным и допустимым для изменения. Часто на производителях таблицы это относится ко времени, необходимому для того, чтобы выходной сигнал достиг 50% от его конечного выходного уровня, когда вход изменяется до 50% от его окончательного входного уровня. Сокращение задержек ворот в цифровые схемы позволяет им обрабатывать данные с большей скоростью и улучшать общую производительность. Определение задержки распространения комбинированной схемы требует определения самого длинного пути задержек распространения от входа до выхода и добавления каждого времени tpd вдоль этого пути.

Разница в задержках распространения логических элементов является основным фактором глюки в асинхронные схемы в результате условия гонки.

В принцип логического усилия использует задержки распространения для сравнения проектов, реализующих один и тот же логический оператор.

Задержка распространения увеличивается с увеличением Рабочая Температура, поскольку сопротивление проводящих материалов имеет тенденцию увеличиваться с температурой. Незначительное увеличение напряжения питания может увеличить задержку распространения, поскольку верхнее пороговое напряжение переключения, ВIH (часто выражается в процентах от шины питания высокого напряжения), естественно, пропорционально увеличивается.[3] Увеличение емкости выходной нагрузки, часто в результате размещения на проводе увеличенных нагрузок разветвления, также увеличивает задержку распространения. Все эти факторы влияют друг на друга через Постоянная времени RC: любое увеличение емкости нагрузки увеличивает C, тепловое сопротивление R-фактор и увеличение порогового напряжения питания влияют на то, требуется ли более одной постоянной времени для достижения порога. Если выход логического элемента подключен к длинной дорожке или используется для управления многими другими воротами (высокий разветвление ) задержка распространения существенно увеличивается.

Провода имеют приблизительную задержку распространения 1 нс на каждые 6 дюймов (15 см) длины.[4] Логические вентили могут иметь задержки распространения от более 10 нс до пикосекундного диапазона, в зависимости от используемой технологии.[4]

Физика

В физика, особенно в электромагнитный В этом поле задержка распространения - это время, необходимое сигналу, чтобы добраться до места назначения. Например, в случае электрического сигнала это время, за которое сигнал проходит по проводу. Смотрите также, коэффициент скорости.

Смотрите также

использованная литература

- ^ «Что такое задержка распространения? (Физический уровень Ethernet)». Часто задаваемые вопросы по Ethernet. 2010-10-21. Получено 2010-11-09.

- ^ «Задержка распространения и ее связь с максимальной длиной кабеля». Сетевой глоссарий. Архивировано из оригинал на 2011-02-20. Получено 2010-11-09.

- ^ «Уровни напряжения логических сигналов». Все о схемах. Получено 1 июня 2016.

- ^ а б Балч, Марк (2003). Mcgraw Hill - Complete Digital Design - Всеобъемлющее руководство по архитектуре цифровой электроники и компьютерных систем. McGraw-Hill Professional. п. 430. ISBN 978-0-07-140927-8.