Источник тока Видлар - Widlar current source

А Источник тока Видлар представляет собой модификацию основных двухкомпонентныхтранзистор текущее зеркало который включает дегенерацию эмиттера резистор только для выходного транзистора, что позволяет источнику тока генерировать малые токи с использованием резистора только умеренных номиналов.[1][2][3]

Схема Видлара может использоваться с биполярные транзисторы, МОП транзисторы, и даже вакуумные трубки. Примером приложения является 741 операционный усилитель,[4] и Видлар использовали эту схему во многих конструкциях.[5]

Эта схема названа в честь ее изобретателя, Боб Видлар, и был запатентован в 1967 году.[6][7]

Анализ

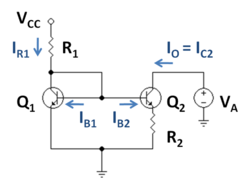

На рисунке 1 показан пример источника тока Видлара на биполярных транзисторах, где эмиттерный резистор R2 подключен к выходному транзистору Q2, и имеет эффект уменьшения тока в Q2 относительно Q1. Ключ к этой схеме в том, что падение напряжения на резисторе р2 вычитает из напряжения база-эмиттер транзистора Q2, тем самым отключив этот транзистор по сравнению с транзистором Q1. Это наблюдение выражается приравниванием выражений базового напряжения, найденных по обе стороны от схемы на Рисунке 1, как:

где β2 - бета-значение выходного транзистора, которое не совпадает с бета-значением входного транзистора, отчасти потому, что токи в двух транзисторах очень разные.[8] Переменная яБи 2 - ток базы выходного транзистора, VБЫТЬ относится к напряжению база-эмиттер. Из этого уравнения следует (используя Закон диода Шокли ):

Уравнение 1

где VТ это тепловое напряжение.

Это уравнение делает приближение того, что токи намного больше, чем масштабные токи, яS1 и яS2; приближение действительно за исключением текущих уровней около отрезать. В дальнейшем предполагается, что токи шкалы идентичны; на практике это нужно специально организовывать.

Методика расчета при заданных токах

Чтобы сконструировать зеркало, выходной ток должен быть связан с двумя номиналами резисторов. р1 и р2. Основное наблюдение заключается в том, что выходной транзистор находится в активный режим только до тех пор, пока его напряжение коллектор-база не равно нулю. Таким образом, простейшее условие смещения для конструкции зеркала устанавливает приложенное напряжение VА чтобы равняться базовому напряжению VB. Это минимальное полезное значение VА называется напряжение соответствия текущего источника. С этим условием смещения Ранний эффект не играет роли в дизайне.[9]

Эти соображения предполагают следующую процедуру проектирования:

- Выберите желаемый выходной ток, яО = яC2.

- Выберите эталонный ток, яR1, предполагается, что он больше, чем выходной ток, вероятно, значительно больше (это цель схемы).

- Определите входной ток коллектора Q1, яC1:

- Определите базовое напряжение VBE1 с использованием Закон диода Шокли

- где яS параметр устройства, иногда называемый масштабный ток.

- Значение базового напряжения также устанавливает напряжение согласования. VА = VBE1. Это самое низкое напряжение, при котором зеркало работает правильно.

- Определять р1:

- Определите сопротивление ноги эмиттера р2 с помощью Уравнение 1 (для уменьшения помех масштабные токи выбираются равными):

Нахождение тока при заданных номиналах резисторов

Обратной задачей проектирования является определение тока, когда известны значения резистора. Далее описывается итерационный метод. Предположим, что источник тока смещен, поэтому напряжение коллектор-база выходного транзистора Q2 равно нулю. Ток через р1 входной или опорный ток, заданный как,

Перестановка, яC1 находится как:

Уравнение 2

Уравнение диода обеспечивает:

Уравнение 3

Уравнение 1 обеспечивает:

Эти три соотношения являются нелинейным, неявным определением токов, которые могут быть решены с помощью итераций.

- Угадываем начальные значения для яC1 и яC2.

- Мы находим значение для VBE1:

- Мы находим новое значение для яC1:

- Мы находим новое значение для яC2:

Эта процедура повторяется до сходимости и удобно настраивается в виде электронной таблицы. Можно просто использовать макрос для копирования новых значений в ячейки электронной таблицы, содержащие начальные значения, чтобы получить решение в короткие сроки.

Обратите внимание, что при показанной схеме, если VCC изменяется, выходной ток изменится. Следовательно, чтобы поддерживать постоянный выходной ток, несмотря на колебания VCC, цепь должна управляться источник постоянного тока вместо того, чтобы использовать резистор р1.

Точное решение

В трансцендентные уравнения выше может быть решена точно с точки зрения W функция Ламберта.

Выходное сопротивление

Важным свойством источника тока является его инкрементный выходной импеданс небольшого сигнала, который в идеале должен быть бесконечным. Схема Видлара использует местную обратную связь по току для транзистора. . Любое увеличение тока в Q2 увеличивает падение напряжения на р2, уменьшая VБЫТЬ за Q2, тем самым противодействуя увеличению тока. Эта обратная связь означает, что выходное сопротивление цепи увеличивается, потому что обратная связь, включающая р2 заставляет использовать большее напряжение для управления заданным током.

Выходное сопротивление определяется с помощью малосигнальной модели схемы, показанной на рисунке 2. Транзистор. Q1 заменяется на его сопротивление излучателя слабого сигнала рE потому что это диодное соединение.[10] Транзистор Q2 заменяется его гибридная пи модель. Тестовый ток яИкс прилагается на выходе.

С помощью рисунка определяется выходное сопротивление по законам Кирхгофа. Используя закон напряжения Кирхгофа от земли слева к заземлению р2:

Перестановка:

Используя закон напряжения Кирхгофа от заземления р2 на землю испытательного тока:

или, заменив яб:

Уравнение 4

Согласно с Уравнение 4, выходное сопротивление источника тока Видлара увеличивается по сравнению с сопротивлением самого выходного транзистора (что составляет рО) пока р2 достаточно большой по сравнению с рπ выходного транзистора (большие сопротивления р2 сделать множитель умножающий рО приближаются к значению (β + 1)). Выходной транзистор пропускает слабый ток, поэтому рπ большой, и увеличение р2 имеет тенденцию к дальнейшему снижению этого тока, вызывая коррелированное увеличение рπ. Таким образом, цель р2 ≫ рπ может быть нереальным, и дальнейшее обсуждение предоставляется ниже. Сопротивление р1∥рE обычно мало, потому что сопротивление эмиттера рE обычно всего несколько Ом.

Текущая зависимость выходного сопротивления

Текущая зависимость сопротивлений рπ и рО обсуждается в статье гибридная пи модель. Текущая зависимость номиналов резисторов:

и

выходное сопротивление из-за Ранний эффект когда VCB = 0 В (параметр устройства VА это раннее напряжение).

Из ранее в этой статье (выставив для удобства токи шкалы равными):Уравнение 5

Следовательно, для обычного случая малых рE, и пренебрегая вторым членом в рО с ожиданием, что главный термин, включающий рО намного больше:Уравнение 6

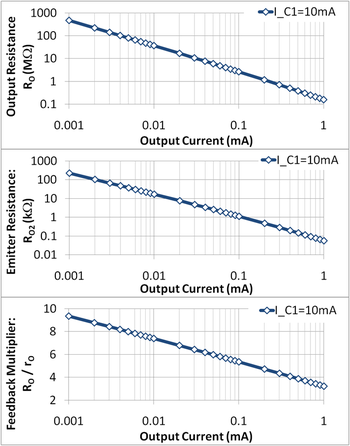

где последняя форма находится заменой Уравнение 5 за р2. Уравнение 6 показывает, что значение выходного сопротивления намного больше, чем рО результатов выходного транзистора только для конструкций с яC1 >> яC2. На рисунке 3 видно, что выходное сопротивление схемы рО определяется не столько обратной связью, сколько текущей зависимостью сопротивления рО выходного транзистора (выходное сопротивление на рис. 3 изменяется на четыре порядка, а коэффициент обратной связи - только на один порядок).

Увеличение в яC1 Увеличение коэффициента обратной связи также приводит к увеличению податливого напряжения, что не очень хорошо, поскольку это означает, что источник тока работает в более ограниченном диапазоне напряжений. Так, например, с целью соответствия установленному напряжению, установив верхний предел для яC1, и с целью достижения выходного сопротивления максимальное значение выходного тока яC2 ограничено.

Центральная панель на Рисунке 3 показывает компромисс между сопротивлением выводов эмиттера и выходным током: меньший выходной ток требует большего резистора ножки и, следовательно, большей площади конструкции. Таким образом, верхняя граница площади устанавливает нижнюю границу выходного тока и верхнюю границу выходного сопротивления схемы.

Уравнение 6 за рО зависит от выбора значения р2 в соответствии с Уравнение 5. Это значит Уравнение 6 это не поведение схемы формула, но расчетное значение уравнение. Один раз р2 выбирается для конкретной цели дизайна, используя Уравнение 5, в дальнейшем его значение фиксируется. Если работа схемы вызывает отклонение токов, напряжений или температур от расчетных значений; затем прогнозировать изменения в рО вызванные такими отклонениями, Уравнение 4 следует использовать, а не Уравнение 6.

Смотрите также

Рекомендации

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Анализ и проектирование аналоговых интегральных схем (4-е изд.). Джон Уайли и сыновья. С. §4.4.1.1 с. 299–303. ISBN 0-471-32168-0.CS1 maint: несколько имен: список авторов (ссылка на сайт)

- ^ А.С. Седра и К.С. Смит (2004). Микроэлектронные схемы (5-е изд.). Издательство Оксфордского университета. Пример 6.14, стр. 654–655. ISBN 0-19-514251-9.

- ^ М. Х. Рашид (1999). Микроэлектронные схемы: анализ и проектирование. PWS Publishing Co., стр. 661–665. ISBN 0-534-95174-0.

- ^ А.С. Седра и К.С. Смит (2004). §9.4.2, с. 899 (5-е изд.). ISBN 0-19-514251-9.

- ^ См., Например, рисунок 2 в Регуляторы напряжения IC.

- ^ RJ Widlar: номер патента США 03320439; Подана 26 мая 1965 г .; Предоставлено 16 мая 1967 г .: Источник маломощного тока для интегральных схем

- ^ См. Видлар: Некоторые методы проектирования схем для линейных интегральных схем и Методы проектирования монолитных операционных усилителей

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Рисунок 2.38, стр. 115. ISBN 0-471-32168-0.CS1 maint: несколько имен: список авторов (ссылка на сайт)

- ^ Конечно, можно представить себе конструкцию, в которой выходное сопротивление зеркала является основным фактором. Тогда нужен другой подход.

- ^ В диодный транзистор коллектор закорочен на базу, поэтому переход коллектор-база транзистора не имеет на нем изменяющегося во времени напряжения. В результате транзистор ведет себя как диод база-эмиттер, который на низких частотах имеет схему слабого сигнала, которая представляет собой просто резистор. рE = VТ / яE, с участием яE DC Q-точка эмиттерный ток. Видеть диодная малосигнальная схема.

дальнейшее чтение

- Линден Т. Харрисон (2005). Источники тока и напряжения: Ссылки A Конструкция Справочник по радиоэлектронике. Elsevier-Newnes. ISBN 0-7506-7752-X.

- Сундарам Натараджан (2005). Микроэлектроника: анализ и дизайн. Тата МакГроу-Хилл. п. 319. ISBN 0-07-059096-6.

- Текущие зеркала и активные нагрузки: Mu-Huo Cheng

![{ displaystyle { begin {align} ( beta _ {2} +1) I_ {B2} & = left (1 + { frac {1} { beta _ {2}}} right) I_ { C2} = { frac {1} {R_ {2}}} left (V_ {BE1} -V_ {BE2} right) & = { frac {V _ { text {T}}} {R_ {2}}} left [ ln left (I_ {C1} / I_ {S1} right) - ln left (I_ {C2} / I_ {S2} right) right] = { frac {V _ { text {T}}} {R_ {2}}} ln left ({ frac {I_ {C1} I_ {S2}} {I_ {C2} I_ {S1}}} right) , end {align}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2fe36a235ecb9c1bd0e3eedd49a6363f645cfeca)

![I_ {b} left [(R_ {1} parallel r_ {E}) + r _ { pi} right] + [I_ {x} + I_ {b}] R_ {2} = 0 .](https://wikimedia.org/api/rest_v1/media/math/render/svg/3862be56e5a63578fd1bf57900a13aedaa94788c)

![R_ {O} = { frac {V_ {x}} {I_ {x}}} = r_ {O} left [1 + { frac { beta R_ {2}} {(R_ {1} parallel r_ {E}) + r _ { pi} + R_ {2}}} right]](https://wikimedia.org/api/rest_v1/media/math/render/svg/d8b1cfc4fd11db5b1b3d090da8cfbd0e592e0095)

![+ R_ {2} left [{ frac {(R_ {1} parallel r_ {E}) + r _ { pi}} {(R_ {1} parallel r_ {E}) + r _ { pi } + R_ {2}}} вправо] .](https://wikimedia.org/api/rest_v1/media/math/render/svg/033a7d64c94712c0e8c1e3cf1bfcd747be5318e7)