Флэш-АЦП - Flash ADC

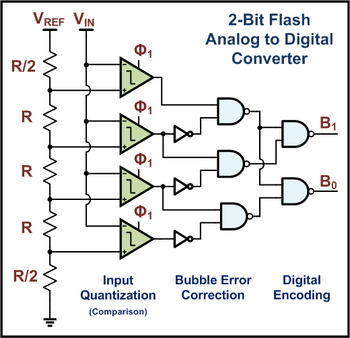

А флэш-АЦП (также известный как АЦП прямого преобразования) является разновидностью аналого-цифровой преобразователь который использует линейный лестница напряжения с компаратор на каждой «ступеньке» лестницы для сравнения входного напряжения с последовательными опорными напряжениями. Часто эти эталонные лестницы состоят из множества резисторы; однако современные реализации показывают, что возможно и емкостное деление напряжения. Выход этих компараторов обычно подается в цифровой кодировщик, который преобразует входные данные в двоичное значение (собранные выходы компараторов можно рассматривать как унарный ценить).

Преимущества и недостатки

Флэш-преобразователи чрезвычайно быстры по сравнению со многими другими типами АЦП, которые обычно сужают "правильный" ответ на серии этапов. По сравнению с ними, флэш-преобразователь также довольно прост и, помимо аналоговых компараторов, требует только логика для окончательного преобразования в двоичный.

Для большей точности часто отслеживание и удержание Схема вставляется перед входом АЦП. Это необходимо для многих типов АЦП (например, АЦП последовательного приближения ), но для флэш-АЦП в этом нет реальной необходимости, потому что компараторы являются устройствами выборки.

Флэш-конвертер требует огромного количества компараторы по сравнению с другими АЦП, особенно по мере увеличения точности. Флэш-конвертер требует компараторы для п-битовое преобразование. Размер, потребляемая мощность и стоимость всех этих компараторов делают флэш-преобразователи практически непрактичными для точности, намного превышающей 8 бит (255 компараторов). Вместо этих компараторов большинство других АЦП заменяют более сложные логика и / или аналоговые схемы, которые можно легко масштабировать для увеличения точность.

Выполнение

Флэш-АЦП реализованы во многих технологиях, начиная от кремниевых. биполярный (BJT) и дополнительный металл-оксид Полевые транзисторы (CMOS ) к редко используемым технологиям III-V технологии. Часто этот тип АЦП используется в качестве первой проверки аналоговой схемы среднего размера.

Самые ранние реализации состояли из эталонной лестницы хорошо согласованных резисторов, подключенных к эталонному напряжению. Каждое нажатие на резисторная лестница используется для одного компаратора, возможно, ему предшествует усиление и, таким образом, генерирует логический 0 или 1 в зависимости от того, находится ли измеренное напряжение выше или ниже опорное напряжение из резистор. Причина, чтобы добавить усилитель имеет два аспекта: он усиливает разность напряжений и, следовательно, подавляет компаратор смещения, и кик-обратно шум компаратора в направлении опорной лестницы также сильно подавлен. Обычно создаются проекты от 4 до 6 бит, а иногда и до 7 бит.

Были продемонстрированы конструкции с энергосберегающими емкостными эталонными лестницами. Помимо тактирования компаратора (ов), эти системы также производят выборку эталонного значения на входном каскаде. Поскольку выборка выполняется с очень высокой скоростью, утечка конденсаторов незначительна.

Недавно в конструкции флэш-АЦП была введена калибровка смещения. Вместо высокоточных аналоговых схем (которые увеличивают размер компонентов для подавления вариаций) измеряются и настраиваются компараторы с относительно большими ошибками смещения. Подается тестовый сигнал, и смещение каждого компаратора калибруется ниже LSB значение АЦП.

Еще одно усовершенствование многих флэш-АЦП - включение цифровой коррекции ошибок. Когда АЦП используется в суровых условиях или построен на основе очень небольших процессов на интегральных схемах, существует повышенный риск того, что один компаратор случайным образом изменит состояние, что приведет к неправильному коду. Коррекция пузырьковых ошибок - это механизм цифровой коррекции, который не позволяет компаратору, который, например, отключил высокий логический уровень, сообщать высокий логический уровень, если он окружен компараторами, которые сообщают низкий логический уровень.

Складной АЦП

Количество компараторов можно несколько уменьшить, добавив спереди складывающуюся цепь, создав так называемую складной АЦП. Вместо того, чтобы использовать компараторы во флэш-АЦП только один раз, во время линейного входного сигнала, складывающийся АЦП повторно использует компараторы несколько раз. Если мсхема складывания в разы используется в п-разрядный АЦП, фактическое количество компаратора может быть уменьшено с к (всегда нужен для определения кроссовера диапазона). Типичными схемами складывания являются Множитель Гилберта и аналог проводное ИЛИ схемы.

Заявление

Очень высокий частота дискретизации АЦП этого типа позволяет использовать высокочастотные приложения (обычно в диапазоне нескольких ГГц), например радар обнаружение широкополосное радио приемники, электронное испытательное оборудование, и оптическая связь ссылки. Чаще всего флэш-АЦП встраивают в большой IC содержащий множество функций цифрового декодирования.

Также небольшая схема АЦП вспышки может присутствовать внутри дельта-сигма модуляция петля.

Флэш-АЦП также используются в NAND flash память, где хранится до 3 бит на клетка как уровень 8 напряжений на плавающих затворах.

Рекомендации

- Аналого-цифровое преобразование

- Понимание Flash ADC

- «Интегрированные аналого-цифровые и цифро-аналоговые преобразователи», Р. ван де Плассе, ADC, Kluwer Academic Publishers, 1994.

- «Точный четырехквадрантный умножитель с субнаносекундным откликом», Барри Гилберт, IEEE Journal of Solid-State Circuits, Vol. 3, № 4 (1968), стр. 365–373