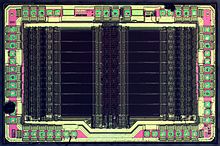

Комплексное программируемое логическое устройство - Complex programmable logic device

Эта статья нужны дополнительные цитаты для проверка. (Ноябрь 2013) (Узнайте, как и когда удалить этот шаблон сообщения) |

А сложное программируемое логическое устройство (CPLD) это программируемое логическое устройство со сложностью между PAL и ПЛИС, и архитектурные особенности обоих. Основным строительным блоком CPLD является макроячейка, который содержит логику, реализующую дизъюнктивная нормальная форма выражения и более специализированные логические операции.

Функции

Некоторые функции CPLD являются общими с PAL:

- Энергонезависимая память конфигурации. В отличие от многих FPGA, внешняя конфигурация ПЗУ не требуется, и CPLD может работать сразу после запуска системы.

- Для многих устаревших устройств CPLD маршрутизация ограничивает большинство логических блоков подключением входных и выходных сигналов к внешним контактам, уменьшая возможности для внутреннего хранения состояния и многоуровневой логики. Обычно это не фактор для больших CPLD и новых семейств продуктов CPLD.

Другие функции являются общими с ПЛИС:

- Доступно большое количество ворот. CPLD обычно имеют эквивалент от тысяч до десятков тысяч логические ворота, позволяющий реализовать умеренно сложные устройства обработки данных. PAL обычно имеют не более нескольких сотен эквивалентов вентилей, в то время как FPGA обычно варьируются от десятков тысяч до нескольких миллионов.

- Некоторые положения для логики более гибкие, чем сумма продукта выражения, включая сложные пути обратной связи между макроячейками и специализированную логику для реализации различных часто используемых функций, таких как целое число арифметика.

Наиболее заметное различие между большим CPLD и маленьким FPGA - наличие энергонезависимой памяти на кристалле в CPLD, что позволяет использовать CPLD для "загрузчик перед передачей управления другим устройствам, не имеющим собственного постоянного хранилища программ. Хорошим примером является использование CPLD для загрузки данных конфигурации для FPGA из энергонезависимой памяти.[1]

Отличия

CPLD были эволюционным шагом от еще более мелких устройств, которые им предшествовали, PLA (сначала отправлено Печатки ), и PAL. Этим, в свою очередь, предшествовали стандартная логика продукты, которые не предлагали программируемости и использовались для построения логических функций путем физического соединения нескольких стандартных логических микросхем (или сотен из них) вместе (обычно с разводкой на печатной плате или платах, но иногда, особенно для прототипирования, с использованием проволока проводка).

Основное различие между архитектурами устройств FPGA и CPLD заключается в том, что FPGA внутренне основаны на справочные таблицы (LUT), в то время как CPLD формируют логические функции с море ворот (например, сумма произведений).

Смотрите также

- Язык:

- Производители:

- Альтера (Теперь Intel)

- Атмель (Теперь Микрочип)

- Cypress Semiconductor

- Решетчатый полупроводник

- Xilinx

- Технологии:

- Интегральная схема для конкретного приложения (ASIC)

- Стираемое программируемое логическое устройство (EPLD)

- Простое программируемое логическое устройство (SPLD)

- Массив макроячеек

- Программируемая логика массива (PAL)

- Программируемая логическая матрица (PLA)

- Программируемое логическое устройство (PLD)

- Общая логика массива (GAL)

- Программируемая электрически стираемая логика (ЧИСТИТЬ)

- Программируемая вентильная матрица (ПЛИС)

внешняя ссылка

Рекомендации

- ^ «Сложное программируемое логическое устройство». blogspot.com. Май 2008 г.. Получено 2013-11-17.