Система на микросхеме - System on a chip

А система на чипе (SoC /ˌɛsˌoʊˈsя/ ес-ой-ВИДЕТЬ или же /sɒk/ носок )[nb 1] является Интегральная схема (также известный как «чип»), который объединяет все или большинство компонентов компьютер или другой электронная система. Эти компоненты почти всегда включают центральное процессорное устройство (ЦПУ), объем памяти, ввод, вывод порты и вторичное хранилище - все на одном субстрат или микрочип размером с монету.[1] Он может содержать цифровой, аналог, смешанный сигнал, и часто радиочастота обработка сигналов функции (в противном случае он считается только процессором приложений).

Высокопроизводительные SoC часто сочетаются с выделенной и физически отдельной памятью и вторичным хранилищем (почти всегда LPDDR и eUFS или же eMMC соответственно) микросхем, которые могут быть наложены поверх SoC в так называемом пакет на пакете (PoP) или размещать рядом с SoC. Кроме того, SoC могут использовать отдельные беспроводные модемы.[2]

SoC в отличие от обычных традиционных материнская плата -основан ПК архитектура, который разделяет компоненты на основе функций и соединяет их через центральную интерфейсную плату.[nb 2] В то время как материнская плата содержит съемные или заменяемые компоненты и соединяет их, SoC объединяют все эти компоненты в единую интегральную схему. SoC обычно объединяет интерфейсы процессора, графики и памяти,[№ 3] подключение жесткого диска и USB,[№ 4] произвольный доступ и только чтение воспоминания и вторичное хранилище на кристалле с одной схемой, тогда как материнская плата будет соединять эти модули как дискретные компоненты или же карты расширения.

SoC объединяет микроконтроллер или же микропроцессор с продвинутыми периферийными устройствами, такими как графический процессор (GPU), Вай фай модуль, или один или несколько сопроцессоры.[3] Подобно тому, как микроконтроллер объединяет микропроцессор с периферийными схемами и памятью, SoC можно рассматривать как интеграцию микроконтроллера с еще более продвинутыми периферийные устройства.

Более тесно интегрированные конструкции компьютерных систем улучшаются спектакль и уменьшить потребляемая мощность а также полупроводниковый кристалл по сравнению с многочиповыми конструкциями с эквивалентной функциональностью. Это происходит за счет уменьшения заменяемость компонентов. По определению, проекты SoC полностью или почти полностью интегрированы в различные компоненты. модули. По этим причинам наблюдается общая тенденция к более тесной интеграции компонентов в промышленность компьютерного оборудования отчасти из-за влияния SoC и уроков, извлеченных из рынков мобильных и встроенных вычислений. SoC можно рассматривать как часть более широкой тенденции к встроенные вычисления и аппаратное ускорение.

SoC очень распространены в Мобильные вычисления (например, в смартфоны ) и периферийные вычисления рынки.[4][5] Они также обычно используются в встроенные системы и Интернет вещей.

Типы

В общем, существует четыре различных типа SoC:

- SoC, построенные на основе микроконтроллер,

- SoC, построенные на основе микропроцессор, часто встречается в мобильных телефонах;

- Специализированный специализированная интегральная схема SoC, предназначенные для конкретных приложений, которые не попадают в две вышеуказанные категории, и

- Программируемые SoC (PSoC), где большинство функций исправлено, но некоторые функции перепрограммируемый аналогично программируемая вентильная матрица.

Приложения

SoC могут быть применены к любой вычислительной задаче. Однако они обычно используются в мобильных вычислениях, таких как планшеты, смартфоны, умные часы и нетбуки, а также встроенные системы и в приложениях, где раньше микроконтроллеры будет использоваться.

Встроенные системы

Там, где раньше можно было использовать только микроконтроллеры, SoC становятся все более популярными на рынке встраиваемых систем. Более тесная системная интеграция обеспечивает лучшую надежность и среднее время наработки на отказ, и SoC предлагают более продвинутую функциональность и вычислительную мощность, чем микроконтроллеры.[6] Приложения включают Ускорение ИИ, встроенный машинное зрение,[7] сбор информации, телеметрия, векторная обработка и окружающий интеллект. Часто встроенные SoC ориентированы на Интернет вещей, промышленный интернет вещей и периферийные вычисления рынки.

Мобильные вычисления

Мобильные вычисления SoC на основе всегда объединяют процессоры, память, на кристалле тайники, беспроводная сеть возможности и часто цифровая камера железо и прошивка. По мере увеличения объема памяти высокопроизводительные SoC часто не имеют памяти и флэш-памяти, а вместо этого используются память и флэш-память будет размещен рядом или выше (пакет на пакете ), SoC.[8] Вот некоторые примеры SoC для мобильных вычислений:

- Samsung Electronics: список, обычно на основе ARM7 и ARM9

- Qualcomm:

- Львиный зев (список ), используемый во многих LG, Xiaomi, Google Pixel, HTC и смартфоны Samsung Galaxy. В 2018 году SoC Snapdragon используются в качестве основы портативные компьютеры Бег Windows 10, позиционируется как «ПК с постоянным подключением».[9][10]

Персональные компьютеры

В 1992 г. Желудь Компьютеры произвел Линейка персональных компьютеров A3010, A3020 и A4000 с ARM250 SoC. Он сочетал в себе оригинальный процессор Acorn ARM2 с контроллером памяти (MEMC), видеоконтроллером (VIDC) и контроллером ввода-вывода (IOC). В предыдущем Желудь РУКА - компьютеры с питанием от четырех дискретных микросхем. Чип ARM7500 был их SoC второго поколения, основанным на контроллерах ARM700, VIDC20 и IOMD, и был широко лицензирован во встроенных устройствах, таких как телевизионные приставки, а также в более поздних персональных компьютерах Acorn.

SoC применяются в основных персональные компьютеры по состоянию на 2018 год.[9] Они особенно применимы к ноутбуки и планшетные ПК. Производители планшетов и ноутбуков извлекли уроки из рынков встраиваемых систем и смартфонов относительно снижения энергопотребления, повышения производительности и надежности за счет более жестких интеграция оборудования и прошивка модули, и LTE и другие беспроводная сеть коммуникации интегрированы на чипе (интегрированы контроллеры сетевого интерфейса ).[11]

РУКА -основан:

x86 -основан:

- Intel Pentium Золото 4415Y, использованное в Microsoft Surface Go

Структура

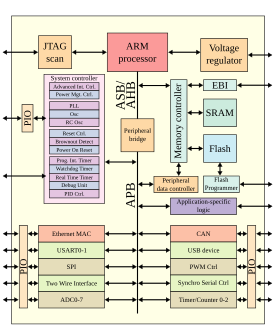

SoC состоит из оборудования функциональные единицы, включая микропроцессоры что запустить программный код, также как и подсистема связи для подключения, управления, направления и взаимодействия между этими функциональными модулями.

Функциональные компоненты

Ядра процессора

SoC должен иметь хотя бы один ядро процессора, но обычно SoC имеет более одного ядра. Ядра процессора могут быть микроконтроллер, микропроцессор (мкП),[12] цифровой сигнальный процессор (DSP) или процессор набора команд для конкретного приложения (ASIP) ядро.[13] ASIP имеют наборы инструкций которые настроены для домен приложения и разработан, чтобы быть более эффективным, чем инструкции общего назначения для определенного типа рабочей нагрузки. Многопроцессорные SoC иметь более одного ядра процессора по определению.

Будь то одноядерный, многоядерный или же многоядерный, Ядра процессора SoC обычно используют RISC архитектуры наборов команд. Архитектура RISC выгоднее CISC процессоры для SoC, потому что они требуют меньше цифровой логики и, следовательно, меньше энергии и площади на доска, а в встроенный и Мобильные вычисления рынки, территория и власть часто сильно ограничены. В частности, ядра процессоров SoC часто используют ARM архитектура потому что это мягкий процессор указано как IP ядро и более энергоэффективен, чем x86.[12]

объем памяти

SoC должны иметь полупроводниковая память блоки для выполнения своих вычислений, как и микроконтроллеры и другие встроенные системы. В зависимости от приложения память SoC может формировать иерархия памяти и иерархия кеша. На рынке мобильных компьютеров это обычное дело, но во многих малая мощность встроенные микроконтроллеры, в этом нет необходимости. Технологии памяти для SoC включают только для чтения памяти (ПЗУ), оперативная память (RAM), электрически стираемое программируемое ПЗУ (EEPROM ) и флэш-память.[12] Как и в других компьютерных системах, оперативную память можно разделить на относительно более быстрые, но более дорогие. статическая RAM (SRAM) и медленнее, но дешевле динамическое ОЗУ (ДРАМ). Когда SoC имеет тайник иерархии, SRAM обычно используется для реализации регистры процессора и ядра ' Кеши L1 тогда как DRAM будет использоваться для более низких уровней иерархии кеша, включая основная память. «Основная память» может относиться к одному процессору (который может быть многоядерный ) когда SoC имеет несколько процессоров, в этом случае это распределенная память и должен быть отправлен через § Межмодульное общение на кристалле для доступа к другому процессору.[13] Для дальнейшего обсуждения проблем с памятью для нескольких процессоров см. согласованность кеша и задержка памяти.

Интерфейсы

SoC включают внешние интерфейсы, обычно для протоколы связи. Они часто основаны на отраслевых стандартах, таких как USB, FireWire, Ethernet, USART, SPI, HDMI, I²C и т. д. Эти интерфейсы будут отличаться в зависимости от предполагаемого приложения. Беспроводная сеть протоколы, такие как Вай фай, Bluetooth, 6LoWPAN и связь ближнего поля также может поддерживаться.

При необходимости SoC включают аналог интерфейсы, включая аналого-цифровой и цифро-аналоговые преобразователи, часто для обработка сигналов. Они могут взаимодействовать с различными типами датчики или же приводы, включая умные преобразователи. Они могут взаимодействовать с конкретным приложением модули или щиты.[№ 5] Или они могут быть внутренними по отношению к SoC, например, если аналоговый датчик встроен в SoC, и его показания должны быть преобразованы в цифровые сигналы для математической обработки.

Цифровые сигнальные процессоры

Цифровой сигнальный процессор (DSP) ядра часто включаются в SoC. Они выполняют обработка сигналов операции в SoC для датчики, приводы, сбор информации, анализ данных и обработка мультимедиа. Ядра DSP обычно имеют очень длинное командное слово (VLIW) и одна инструкция, несколько данных (SIMD) архитектуры наборов команд, и, следовательно, очень подвержены эксплуатации параллелизм на уровне инструкций через параллельная обработка и суперскалярное исполнение.[13]:4 Ядра DSP чаще всего содержат инструкции, специфичные для приложения, и как таковые обычно процессоры с набором команд для конкретных приложений (ГЛОТОК). Такие специфические для приложения инструкции соответствуют выделенному оборудованию. функциональные единицы которые вычисляют эти инструкции.

Типичные инструкции DSP включают: умножать-накапливать, Быстрое преобразование Фурье, слитное умножение-сложение, и извилины.

Другой

Как и в случае с другими компьютерными системами, SoC требуют источники времени чтобы генерировать тактовые сигналы, контролировать выполнение функций SoC и предоставлять временной контекст для обработка сигналов приложения SoC, если необходимо. Популярные источники времени: кварцевые генераторы и петли фазовой автоподстройки частоты.

SoC периферийные устройства включая прилавок -таймеры, в реальном времени таймеры и сброс при включении генераторы. SoC также включают регуляторы напряжения и управление энергопотреблением схемы.

Межмодульное общение

SoC включают в себя множество исполнительные единицы. Эти подразделения должны часто отправлять данные и инструкции взад и вперед. Из-за этого все, кроме самых тривиальных SoC, требуют подсистемы связи. Первоначально, как и у других микрокомпьютер технологии, шина данных использовались разные архитектуры, но недавно были разработаны проекты, основанные на разреженных сетях связи, известных как сети на кристалле (NoC) приобрели известность и, по прогнозам, в ближайшем будущем обгонят автобусные архитектуры для проектирования SoC.[14]

Связь по шине

Исторически сложилось так, что общая глобальная компьютерный автобус обычно соединяются различные компоненты, также называемые «блоками» SoC.[14] Очень распространенная шина для связи SoC - это бесплатная архитектура шины микроконтроллера ARM (AMBA ) стандарт.

Прямой доступ к памяти контроллеры направляют данные напрямую между внешними интерфейсами и памятью SoC, минуя ЦП или устройство управления, тем самым увеличивая данные пропускная способность SoC. Это похоже на некоторые драйверы устройств периферии на компонентной основе многокристальный модуль Архитектура ПК.

Компьютерные автобусы ограничены в масштабируемость, поддерживающая до десятков ядер (многоядерный ) на одном чипе.[14]:xiii Задержка провода не масштабируется из-за продолжающегося миниатюризация, производительность системы не масштабируется с количеством подключенных ядер, SoC рабочая частота должен уменьшаться с каждым дополнительным подключенным сердечником, чтобы питание было устойчивым, а длинные провода потребляют большое количество электроэнергии. Эти проблемы недопустимы для поддержки многоядерный системы на чипе.[14]:xiii

Сеть на микросхеме

В конце 2010-е, тенденция внедрения SoC подсистемы связи с точки зрения сетевой топологии вместо автобусный протоколы появились. Тенденция к больше процессорных ядер на SoC привело к тому, что эффективность связи на кристалле стала одним из ключевых факторов, определяющих общую производительность и стоимость системы.[14]:xiii Это привело к появлению сетей межсетевого взаимодействия с маршрутизатор -основан коммутация пакетов известный как "сети на чипе "(NoCs) для преодоления узкие места шинных сетей.[14]:xiii

Сети на кристалле имеют преимущества, в том числе зависящие от места назначения и приложения. маршрутизация, повышенная энергоэффективность и сниженная вероятность автобусный спор. Архитектура "сеть на кристалле" вдохновлена сетевые протоколы подобно TCP и Набор интернет-протоколов для внутрикристальной коммуникации,[14] хотя обычно у них меньше сетевые уровни. Оптимальная сеть на кристалле сетевые архитектуры являются постоянной областью большого исследовательского интереса. Архитектуры NoC варьируются от традиционных распределенных вычислений сетевые топологии Такие как тор, гиперкуб, сетки и древовидные сети к планирование генетического алгоритма к рандомизированные алгоритмы Такие как случайные блуждания с ветвлением и рандомизированный время жить (TTL).

Многие исследователи SoC считают архитектуры NoC будущим дизайна SoC, поскольку было показано, что они эффективно удовлетворяют потребности в мощности и пропускной способности конструкций SoC. Современные архитектуры NoC двумерны. 2D дизайн ИС ограничен планировка этажа выбор по мере увеличения количества ядер в SoC, так что трехмерные интегральные схемы (3DIC) дизайнеры SoC стремятся построить трехмерные сети на кристалле, известные как 3DNoC.[14]

Дизайн-поток

Эта секция нужны дополнительные цитаты для проверка. (Март 2017 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

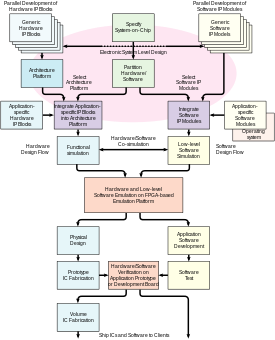

Система на микросхеме состоит из аппаратное обеспечение, описанный в § Структура, а программного обеспечения управление микроконтроллером, микропроцессором или ядрами процессора цифровых сигналов, периферийными устройствами и интерфейсами. В расчетный поток for SoC направлена на одновременную разработку этого оборудования и программного обеспечения, также известную как совместное архитектурное проектирование. В процессе проектирования также должны учитываться оптимизации (§ Цели оптимизации ) и ограничения.

Большинство SoC разрабатываются из предварительно проверенных аппаратных компонентов. Характеристики IP ядра для элементов оборудования и исполнительные единицы, совместно "блоки", описанные выше, вместе с программным обеспечением драйверы устройств которые могут контролировать их работу. Особое значение имеют стеки протоколов которые управляют стандартными отраслевыми интерфейсами, такими как USB. Аппаратные блоки собираются вместе с использованием системы автоматизированного проектирования инструменты, в частности автоматизация проектирования электроники инструменты; то программные модули интегрированы с помощью программного обеспечения интегрированная среда развития.

Компоненты SoC также часто разрабатываются в языки программирования высокого уровня Такие как C ++, MATLAB или же SystemC и преобразован в RTL дизайн через синтез высокого уровня (HLS), такие как C в HDL или же поток к HDL.[15] Продукты HLS, называемые «алгоритмическим синтезом», позволяют разработчикам использовать C ++ для моделирования и синтеза систем, схем, программного обеспечения и уровней проверки на одном языке высокого уровня, широко известном в мире. компьютерные инженеры способом, не зависящим от масштабов времени, которые обычно указываются в HDL.[16] Остальные компоненты могут оставаться программными и могут быть скомпилированы и встроены в soft-core процессоры включены в SoC как модули в HDL как IP ядра.

Однажды архитектура SoC, любые новые аппаратные элементы записываются абстрактно язык описания оборудования названный зарегистрировать уровень передачи (RTL), который определяет поведение схемы, или синтезируется в RTL из языка высокого уровня посредством синтеза высокого уровня. Эти элементы соединены вместе на языке описания оборудования для создания полного дизайна SoC. Логика, указанная для соединения этих компонентов и преобразования между, возможно, разными интерфейсами, предоставляемыми разными поставщиками, называется клей логика.

Проверка дизайна

Чипы проверяются на логическую правильность перед отправкой в литейное производство полупроводников. Этот процесс называется функциональная проверка и на него приходится значительная часть времени и энергии, затрачиваемых на жизненный цикл дизайна микросхемы, часто указывается как 70%.[17][18] С ростом сложности микросхем, языки проверки оборудования подобно SystemVerilog, SystemC, е, и OpenVera используются. Ошибки обнаруженные на этапе проверки доводятся до дизайнера.

Традиционно инженеры использовали ускорение моделирования, подражание или прототипирование на перепрограммируемое оборудование для проверки и отладки оборудования и программного обеспечения для проектов SoC до завершения проекта, известного как клейкая лента. Программируемые вентильные матрицы (FPGA) предпочтительны для прототипирования SoC, потому что Прототипы ПЛИС перепрограммируемы, позволяют отладка и более гибкие, чем специализированные интегральные схемы (ASIC).[19][20]

Благодаря высокой емкости и быстрому времени компиляции, ускорение моделирования и эмуляция являются мощными технологиями, обеспечивающими широкий обзор систем. Обе технологии, однако, работают медленно, порядка МГц, что может быть значительно медленнее - до 100 раз медленнее - чем рабочая частота SoC. Блоки ускорения и эмуляции также очень большие и дорогие - более 1 миллиона долларов США.[нужна цитата ]

Прототипы FPGA, напротив, используют FPGA напрямую, чтобы дать инженерам возможность проверять и тестировать на полной рабочей частоте системы или близкой к ней с реальными воздействиями. Такие инструменты, как Certus[21] используются для вставки зондов в RTL FPGA, которые делают сигналы доступными для наблюдения. Это используется для отладки взаимодействия аппаратного, микропрограммного и программного обеспечения между несколькими ПЛИС с возможностями, аналогичными логическому анализатору.

Параллельно с этим элементы оборудования группируются и проходят через процесс логический синтез, во время которого применяются ограничения производительности, такие как рабочая частота и ожидаемые задержки сигнала. Это генерирует вывод, известный как список соединений описание конструкции как физической схемы и ее взаимосвязей. Эти списки соединений объединены с клей логика соединение компонентов для создания схематического описания SoC как цепи, которая может быть напечатанный на чип. Этот процесс известен как место и маршрут и предшествует клейкая лента в случае, если SoC производятся как специализированные интегральные схемы (ASIC).

Цели оптимизации

SoC должны оптимизировать использование энергии, площадь на умереть, общение, позиционирование для местонахождение между модульными установками и другими факторами. Оптимизация обязательно является целью разработки SoC. Если в оптимизации не было необходимости, инженеры использовали бы многокристальный модуль архитектура без учета использования площади, энергопотребления или производительности системы в той же степени.

Далее следуют общие цели оптимизации для проектов SoC с объяснениями каждой из них. В общем, оптимизация любого из этих количеств может быть сложной задачей. комбинаторная оптимизация проблема, и действительно может быть NP-жесткий довольно легко. Следовательно, сложные алгоритмы оптимизации часто требуются, и может быть полезно использовать аппроксимационные алгоритмы или же эвристика в некоторых случаях. Кроме того, большинство проектов SoC содержат несколько переменных для одновременной оптимизации, так Парето эффективный решения востребованы в дизайне SoC. Часто цели оптимизации некоторых из этих количеств прямо расходятся, что еще больше усложняет оптимизацию дизайна SoC и вводит компромиссы в системном дизайне.

Для более широкого охвата компромиссов и анализ требований, видеть разработка требований.

Цели

Потребляемая мощность

SoC оптимизированы для минимизации электричество используется для выполнения функций SoC. Большинство SoC должны использовать низкое энергопотребление. Системы SoC часто требуют длительного срок службы батареи (Такие как смартфоны ), потенциально могут проводить месяцы или годы без источника питания, которому необходимо поддерживать автономную работу, и часто ограничиваются в потреблении энергии большим количеством встроенный SoC являются объединены в сеть в районе. Кроме того, затраты на электроэнергию могут быть высокими, а экономия энергии снизит Общая стоимость владения SoC. Ну наконец то, отходящее тепло из-за высокого потребления энергии может повредить другие компоненты схемы, если рассеивается слишком много тепла, что дает еще одну прагматическую причину для экономии энергии. Количество энергия в цепи используется интеграл из мощность расходуется по времени, а Средняя оценка потребляемой мощности является продуктом Текущий к Напряжение. Эквивалентно Закон Ома, мощность - это квадрат тока, умноженный на сопротивление, или квадрат напряжения, деленный на сопротивление:

Производительность на ватт

SoC оптимизированы для максимизации энергоэффективность в производительности на ватт: максимизируйте производительность SoC с учетом бюджета энергопотребления. Многие приложения, такие как периферийные вычисления, распределенная обработка и окружающий интеллект требуется определенный уровень вычислительная производительность, но мощность ограничена в большинстве сред SoC. В ARM архитектура имеет большую производительность на ватт, чем x86 во встроенных системах, поэтому он предпочтительнее x86 для большинства приложений SoC, требующих встроенный процессор.

Отработанное тепло

Конструкции SoC оптимизированы для минимизации отходящее тепло выход на чипе. Как и в случае с другими интегральные схемы, тепло, выделяемое из-за высокой удельная мощность являются горлышко бутылки для дальнейшего миниатюризация компонентов.[22]:1 Плотность мощности высокоскоростных интегральных схем, особенно микропроцессоров, включая SoC, стала очень неравномерной. Слишком много отработанного тепла может повредить цепи и вызвать эрозию надежность схемы с течением времени. Высокие температуры и термическое напряжение отрицательно сказываются на надежности, миграция напряжения, уменьшилось среднее время наработки на отказ, электромиграция, проводное соединение, метастабильность и другое снижение производительности SoC со временем.[22]:2–9

В частности, большинство SoC находятся в небольшой физической области или объеме, и поэтому эффекты отработанного тепла усугубляются, потому что у него мало места для его выхода из системы. Из-за высокого количество транзисторов на современных устройствах из-за Закон Мура, часто макет с достаточной пропускной способностью и высокой плотность транзисторов физически осуществимо из производственные процессы но приведет к недопустимо высокому количеству тепла в объеме контура.[22]:1

Эти тепловые эффекты вынуждают разработчиков SoC и других микросхем применять консервативные решения. расчетные поля, создавая менее производительные устройства, чтобы снизить риск катастрофический провал. Из-за увеличения плотности транзисторов по мере уменьшения масштабов длины каждый генерация процесса производит больше тепла, чем предыдущий. Эту проблему усугубляет то, что архитектуры SoC обычно неоднородны, что создает неоднородность в пространстве. тепловые потоки, которые не могут быть эффективно смягчены единообразными пассивное охлаждение.[22]:1

Пропускная способность

Эта секция нуждается в расширении. Вы можете помочь добавляя к этому. (Октябрь 2018 г.) |

SoC оптимизированы для максимизации вычислений и коммуникаций пропускная способность.

Задержка

Эта секция нуждается в расширении. Вы можете помочь добавляя к этому. (Октябрь 2018 г.) |

SoC оптимизированы для минимизации задержка для некоторых или всех их функций. Этого можно добиться выкладывание элементы с надлежащей близостью и местонахождение друг к другу, чтобы минимизировать задержки при подключении и максимизировать скорость, с которой данные передаются между модулями, функциональные единицы и воспоминания. В целом оптимизация для минимизации задержки - это НП-полный проблема эквивалентна проблема логической выполнимости.

За задачи работает на ядрах процессора, задержку и пропускную способность можно улучшить с помощью планирование задач. Однако некоторые задачи выполняются в аппаратных единицах, зависящих от приложения, и даже планирования задач может быть недостаточно для оптимизации всех программных задач в соответствии с ограничениями по времени и пропускной способности.

Методологии

Эта секция нуждается в расширении. Вы можете помочь добавляя к этому. (Октябрь 2018 г.) |

Системы на кристалле моделируются со стандартным оборудованием верификация и валидация методы, но дополнительные методы используются для моделирования и оптимизации альтернатив проектирования SoC, чтобы сделать систему оптимальной в отношении многокритериальный анализ решений по вышеуказанным целям оптимизации.

Планирование задач

Планирование задач это важный вид деятельности в любой компьютерной системе с несколькими процессы или же потоки совместное использование одного ядра процессора. Важно уменьшить § Задержка и увеличить § Пропускная способность за встроенное программное обеспечение работает на SoC § Ядра процессора. Не все важные вычислительные действия в SoC выполняются в программном обеспечении, работающем на процессорах на кристалле, но планирование может значительно улучшить производительность программных задач и других задач, связанных с общие ресурсы.

SoC часто планируют задачи в соответствии с сетевое планирование и рандомизированное планирование алгоритмы.

Конвейерная обработка

Аппаратные и программные задачи часто конвейеризируются в дизайн процессора. Конвейерная обработка - важный принцип для ускорение в компьютерная архитектура. Они часто используются в GPU (графический конвейер ) и процессоры RISC (эволюция классический конвейер RISC ), но также применяются к задачам, связанным с конкретным приложением, таким как цифровая обработка сигналов и мультимедийные манипуляции в контексте SoC.[13]

Вероятностное моделирование

SoC часто анализируются, хотя вероятностные модели, Теория массового обслуживания § Сети массового обслуживания и Цепи Маркова. Например, Закон Литтла позволяет моделировать состояния SoC и буферы NoC как процессы прибытия и анализировать с помощью Пуассоновские случайные величины и Пуассоновские процессы.

Цепи Маркова

SoC часто моделируются с помощью Цепи Маркова, обе дискретное время и непрерывное время варианты. Моделирование цепей Маркова позволяет асимптотический анализ SoC распределение в устойчивом состоянии мощности, тепла, задержки и других факторов, позволяющих оптимизировать проектные решения для общего случая.

Изготовление

Эта секция нужны дополнительные цитаты для проверка. (Март 2017 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

Чипы SoC обычно сфабрикованный с помощью металл – оксид – полупроводник (MOS) технология.[23] Описанные выше списки соединений используются в качестве основы для физического проектирования (место и маршрут ) для преобразования намерений дизайнеров в дизайн SoC. В ходе этого процесса преобразования конструкция анализируется с помощью статического временного моделирования, моделирования и других инструментов, чтобы убедиться, что она соответствует указанным рабочим параметрам, таким как частота, потребляемая мощность и рассеиваемая мощность, функциональная целостность (как описано в коде уровня передачи регистров) и электрические параметры. честность.

Когда все известные ошибки были исправлены, и они были повторно проверены, и все проверки физической конструкции выполнены, файлы физического дизайна, описывающие каждый слой чипа, отправляются в цех масок литейного производства, где будет вытравлен полный набор стеклянных литографических масок. . Они отправляются на завод по производству пластин для создания кристаллов SoC перед упаковкой и тестированием.

SoC могут изготавливаться по нескольким технологиям, включая:

- Полный кастом ASIC

- Стандартная ячейка ASIC

- Программируемая вентильная матрица (ПЛИС)

ASIC потребляют меньше энергии и быстрее, чем FPGA, но не могут быть перепрограммированы и дороги в производстве. Проекты FPGA больше подходят для проектов меньшего объема, но после выпуска достаточного количества единиц ASIC снижают общую стоимость владения.[24]

Конструкции SoC потребляют меньше энергии, имеют более низкую стоимость и более высокую надежность, чем многокристальные системы, которые они заменяют. С меньшим количеством пакетов в системе также снижаются затраты на сборку.

Однако, как и большинство очень крупномасштабная интеграция (СБИС) конструкции, общая стоимость[требуется разъяснение ] выше для одного большого чипа, чем для той же функциональности, распределенной по нескольким меньшим чипам, из-за более низкая урожайность[требуется разъяснение ] и выше разовая инженерия расходы.

Когда невозможно построить SoC для конкретного приложения, альтернативой является система в пакете (SiP), состоящий из нескольких микросхем в одном упаковка. При производстве больших объемов SoC более рентабельна, чем SiP, потому что ее упаковка проще.[25] Еще одна причина, по которой SiP может быть предпочтительнее, - отходящее тепло может быть слишком высоким в SoC для данной цели, потому что функциональные компоненты расположены слишком близко друг к другу, а в SiP тепло будет лучше рассеиваться от разных функциональных модулей, поскольку они физически находятся дальше друг от друга.

Контрольные точки

Эта секция нуждается в расширении. Вы можете помочь добавляя к этому. (Октябрь 2018 г.) |

SoC исследования и разработки часто сравнивает множество вариантов. Тесты, такие как COSMIC,[26] разработаны, чтобы помочь таким оценкам.

Смотрите также

- Список поставщиков системы на кристалле

- Пост-силиконовая проверка

- ARM архитектура

- Одноплатный компьютер

- Система в пакете

- Сеть на микросхеме

- Программируемый SoC

- Процессор набора команд для конкретного приложения (ГЛОТОК)

- Платформенный дизайн

- Лаборатория на чипе

- Орган на микросхеме в биомедицинских технологиях

Примечания

- ^ В этой статье используется условное обозначение SoC произносится как /ˌɛsˌoʊˈsя/ ес-ой-ВИДЕТЬ. Поэтому для обозначения неопределенный артикль соответствующий SoC ("ан SoC "). Другие источники могут произносить это как /sɒk/ носок и поэтому используйте "а SoC ».

- ^ Эта центральная плата называется «материнской платой» для размещения «дочерних» компонентных плат.

- ^ Графические соединения (PCI Express ) и RAM исторически составляли Северный мост дискретных архитектур на материнской плате.

- ^ Жесткий диск и USB-подключение исторически составляли часть южный мост дискретных модульных архитектур на материнской плате.

- ^ В встроенные системы, "щиты" аналогичны карты расширения за ПК. Они часто подходят микроконтроллер например, Ардуино или же одноплатный компьютер такой как Raspberry Pi и функционируют как периферийные устройства для устройства.

Рекомендации

- ^ Шах, Агам (3 января 2017 г.). «7 потрясающих улучшений смартфона с чипом Qualcomm Snapdragon 835». Сетевой мир.

- ^ https://arstechnica.com/gadgets/2020/02/qualcomms-snapdragon-x60-promises-smaller-5g-modems-in-2021/?amp=1

- ^ Миттал, Спарш. «Обзор оптимизированной реализации моделей глубокого обучения на платформе NVIDIA Jetson». Журнал системной архитектуры. ISSN 1383-7621.

- ^ Пит Беннетт, EE Times. "Почему, где и что из конструкции SoC с низким энергопотреблением. "2 декабря 2004 г. Проверено 28 июля 2015 г.

- ^ Нолан, Стивен М. «Разработка системы управления питанием для Интернета вещей (IoT) на кристалле (SoC)». Дизайн и повторное использование. Получено 2018-09-25.

- ^ «Подходит ли однокристальный процессор SOC для вашего встраиваемого проекта?». Встроенный. Получено 2018-10-13.

- ^ «Qualcomm выпускает SoC для встраиваемого зрения | Обработка изображений и машинное зрение в Европе». www.imveurope.com. Получено 2018-10-13.

- ^ «Разборка Samsung Galaxy S10 и S10e». я чиню это. 6 марта 2019.

- ^ а б «ARM идет вслед за Intel с новой дорожной картой чипов до 2020 года». Windows Central. Получено 2018-10-06.

- ^ а б «ПК с постоянным подключением, ноутбуки с увеличенным сроком службы батареи 4G LTE | Windows». www.microsoft.com. Получено 2018-10-06.

- ^ "Сотовые модемы Gigabit Class LTE, 4G LTE и 5G | Qualcomm". Qualcomm. Получено 2018-10-13.

- ^ а б c Фербер, Стивен Б. (2000). Архитектура системы на кристалле ARM. Харлоу, Англия: Эддисон-Уэсли. ISBN 0201675196. OCLC 44267964.

- ^ а б c d е Харис Джавид, Шри Парамешваран (2014). Конвейерная многопроцессорная система на кристалле для мультимедиа. Springer. ISBN 9783319011134. OCLC 869378184.CS1 maint: использует параметр авторов (связь)

- ^ а б c d е ж грамм час Кунду, Сантану; Чаттопадхьяй, Сантану (2014). Сеть на кристалле: новое поколение интеграции системы на кристалле (1-е изд.). Бока-Ратон, Флорида: CRC Press. ISBN 9781466565272. OCLC 895661009.

- ^ "Лучшие практики прототипирования алгоритмов MATLAB и Simulink на ПЛИС". EEJournal. 2011-08-25. Получено 2018-10-08.

- ^ Бойер, Брайан (2005-02-05). «Почему и что» алгоритмического синтеза ». EE Times. Получено 2018-10-08.

- ^ EE Times. "Неужели проверка на 70 процентов?. »14 июня 2004 г. Проверено 28 июля 2015 г.

- ^ «Разница между верификацией и валидацией». Класс тестирования программного обеспечения. Получено 2018-04-30.

Во время интервью большинство интервьюеров задают вопросы на тему «В чем разница между верификацией и валидацией?» Многие люди используют верификацию и валидацию как синонимы, но оба имеют разное значение.

- ^ Риттман, Дэнни (05.01.2006). «Нанометрическое прототипирование» (PDF). Тайден Дизайн. Получено 2018-10-07.

- ^ «Создание прототипа ПЛИС для производства структурированных ASIC для снижения затрат, рисков и TTM». Дизайн и повторное использование. Получено 2018-10-07.

- ^ Брайан Бейли, EE Times. "Tektronix надеется перевернуть прототипы ASIC. "30 октября 2012 г. Проверено 28 июля 2015 г.

- ^ а б c d Огренчи-Мемик, Седа (2015). Управление теплом в интегральных схемах: мониторинг и охлаждение на уровне кристалла и системы. Лондон, Соединенное Королевство: Институт инженерии и технологий. ISBN 9781849199353. OCLC 934678500.

- ^ Лин, Юн-Лонг Стив (2007). Основные вопросы проектирования SOC: проектирование сложных систем на кристалле. Springer Science & Business Media. п. 176. ISBN 9781402053528.

- ^ «FPGA против ASIC: различия между ними и какой из них использовать? - Справочный центр Numato Lab». numato.com. Получено 2018-10-17.

- ^ EE Times. "Великая дискуссия: SOC против SIP. "21 марта 2005 г. Проверено 28 июля 2015 г.

- ^ "КОСМИКА". www.ece.ust.hk. Получено 2018-10-08.

дальнейшее чтение

- Бадави, Ваэль; Джуллиен, Грэм А., ред. (2003). Система на кристалле для приложений реального времени. Международная серия Kluwer в области инженерии и информатики, SECS 711. Бостон: Kluwer Academic Publishers. ISBN 9781402072543. OCLC 50478525. 465 страниц.

- Фурбер, Стивен Б. (2000). Архитектура системы на кристалле ARM. Бостон: Эддисон-Уэсли. ISBN 0-201-67519-6.

- Кунду, Сантану; Чаттопадхьяй, Сантану (2014). Сеть на кристалле: новое поколение интеграции системы на кристалле (1-е изд.). Бока-Ратон, Флорида: CRC Press. ISBN 9781466565272. OCLC 895661009.

внешняя ссылка

- SOCC Ежегодный IEEE Международная конференция SoC

- Бая бесплатный инструмент для сборки платформы SoC и интеграции IP

- Системы на кристалле для встраиваемых приложений, Обернский университет семинар в СБИС

- Мгновенный SoC SoC для FPGA, определенных C ++